#### US006714178B2

# (12) United States Patent

Koyama et al.

# (10) Patent No.: US 6,714,178 B2

(45) **Date of Patent:** Mar. 30, 2004

# (54) **DISPLAY DEVICE**

(75) Inventors: Jun Koyama, Kanagawa (JP); Hajime

Kimura, Kanagawa (JP)

(73) Assignee: Semiconductor Energy Laboratory

Co., Ltd. (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 187 days.

(21) Appl. No.: 09/850,650

(22) Filed: May 7, 2001

(65) **Prior Publication Data**

US 2001/0043168 A1 Nov. 22, 2001

# (30) Foreign Application Priority Data

| (30) | Foreign Application Priority Data           |

|------|---------------------------------------------|

| May  | 12, 2000 (JP) 2000-140513                   |

| (51) | Int. Cl. <sup>7</sup>                       |

| (52) | <b>U.S. Cl. 345/76</b> ; 345/45; 315/169.1; |

|      | 315/169.4                                   |

| (58) | <b>Field of Search</b>                      |

|      | 345/76, 87, 92; 315/169.1, 169.2, 169.3,    |

|      | 169.4                                       |

### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,440,208 | Α          | * | 8/1995  | Uskali et al          |

|-----------|------------|---|---------|-----------------------|

| 5,670,792 | Α          | * | 9/1997  | Utsugi et al 257/59   |

| 6,421,034 | B1         | * | 7/2002  | Mihara 345/76         |

| 6,476,419 | <b>B</b> 1 | * | 11/2002 | Yasuda 257/72         |

| 6,512,504 | <b>B</b> 1 | * | 1/2003  | Yamauchi et al 345/87 |

| 6,529,178 | B1         | * | 3/2003  | Kimura 345/76         |

| 6,556,177 | B1         | * | 4/2003  | Katayama et al 345/76 |

| 6,580,408 | B1         | * | 6/2003  | Bae et al 345/76      |

| 6,580,409 | B1         | * | 6/2003  | Ito et al 345/76      |

|           |            |   |         |                       |

### FOREIGN PATENT DOCUMENTS

| JP | 10-092576   | 4/1998 |

|----|-------------|--------|

| JP | 10-247735   | 9/1998 |

| JP | 2000-242196 | 9/2000 |

#### OTHER PUBLICATIONS

Schenk, H. et al, "Polymers for Light Emitting Diodes," EURODISPLAY '99, Proceedings of the 19th International Display Research Conference, Berlin, Germany, Sep. 6–9, 1999, pp. 33–37, 1999.

English abstract re Japanese Patent Application No. 10–092576, published Apr. 10, 1998.

English abstract re Japanese Patent Application No. 10–247735, published Sep. 14, 1998.

English abstract re Japanese Patent Application No. 2000–242196, published Sep. 8, 2000.

\* cited by examiner

Primary Examiner—Richard Hjerpe

Assistant Examiner—Kimnhung Nguyen

(74) Attorney, Agent, or Firm—Cook, Alex, McFarron, Manzo, Cummings & Mehler, Ltd.

#### (57) ABSTRACT

There is provided an active matrix EL display device that can display a clear multi gray-scale color display to reduce the shift in the potential caused by the potential drop due to the wiring resistance of a power source supply line, in order to decrease the unevenness in a display region. A plurality of drawing out ports of the power source supply line are arranged. Further, in the wiring resistance between the external input terminal and the pixel portion power source supply line, potential compensation is performed by supplying potential to the power source supply line by a feedback amplifier. Further, in addition to above structure, the power source supply line may be arranged in a matrix.

## 28 Claims, 41 Drawing Sheets

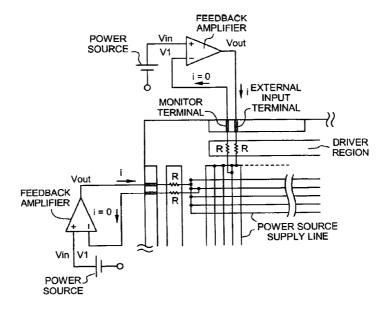

INPUT PORTION FOR POWER SUPPLY LINES 2

**FU**匠. 2

**斯瓜**. 3

IF [[]]. 5

**IF**□**□□**. 6B

FUG. 7B

FIG. 10

Mar. 30, 2004

IF [[]]. 16

FIG. 18 PRIOR ART

IFIIG. 20 PRIOR ART

IF III. 24 PRIOR ART

Mar. 30, 2004

IF II II. 39

FUG. 40 PRIOR ART

F0伝.41 PRIOR ART

FIG. 42

IF [[G. 43]

IF [[G. 44

F0G. 45

#### **DISPLAY DEVICE**

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to an electronic display (electro optical device) formed by fabricating an EL (electro luminescence) element on a substrate. Particularly, the present invention relates to a display device using a semiconductor element (an element employing a semiconductor thin film), and furthermore to electronic equipment using the EL display device as a display portion.

#### 2. Description of the Related Art

In recent years, remarkable progress has been made in a 15 technique for forming thin film transistors (hereinafter referred to as TFTs) on a substrate, and developing the application of TFTs to an active matrix display device is proceeding. TFTs using a polycrystalline semiconductor film such as poly-silicon film, in particular, have a higher 20 electric field effect mobility (also referred to as mobility) than that of conventional TFTs using an amorphous semiconductor film such as an amorphous silicon film, and hence a high speed operation may be made. Thus, control of pixels, which in the past has been controlled by a driver circuit 25 external to a substrate, can now be made by driver circuits formed on the same substrate as the pixels.

Various merits such as reduction of manufacturing cost, miniaturization of a display device, and increase of yield and reduction of throughput can be obtained from such an active matrix display device using a polycrystalline semiconductor film by forming various circuits and elements on the same substrate.

A research on active matrix EL display devices having an EL element as a self-luminous element is being actively carried out. The EL display device is also referred to as an organic EL display (OLED) or an organic light emitting diode (OLED).

The EL element has a structure composed of a pair of electrodes (anode and cathode) and an EL layer, which is usually a laminate structure, sandwiched therebetween. The laminate structure (hole transporting layer, light-emitting layer, electron transporting layer) proposed by Tang, et al. from Eastman Kodak Company can be cited as a typical laminate structure of the EL layer. This laminate structure has an extremely high luminescence efficiency, and therefore at present, most of the EL display devices in which research and development are proceeding adopt this laminate structure of the EL layer.

In addition to the above laminate structure, a structure in which the layers are laminated on the anode in the order of a hole injection layer, a hole transporting layer, a light-emitting layer, and an electron transporting layer or in the order of a hole injection layer, a hole transporting layer, a light-emitting layer, an electron transporting layer, and an electron injection layer may be formed. The light-emitting layer may be doped with a fluorescent pigment or the like.

The EL layer is a generic term in the present specification indicating all the layers formed between the cathode and anode. Therefore, the above-mentioned hole injection layer, the hole transporting layer, the light-emitting layer, the electron transporting layer, the electron injection layer, etc. are all included in the EL layer.

If a predetermined voltage from the pair of electrodes is 65 applied to the EL layer having the above structure, a re-coupling of carriers in the light-emitting layer occurs to

2

thereby emit light. It is to be noted that throughout the present specification, the emission of light by the EL element is called a drive by the EL element. In addition, a luminescent element formed of the anode, the EL layer, and the cathode is called the EL element in the present specification.

It is to be noted that an EL element as used herein includes one utilizing light emission from singlet excited state (fluorescence) and one utilizing light emission from triplet excited state (phosphorescence).

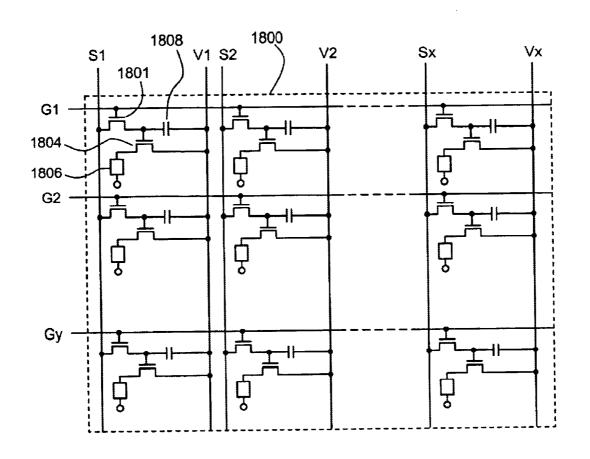

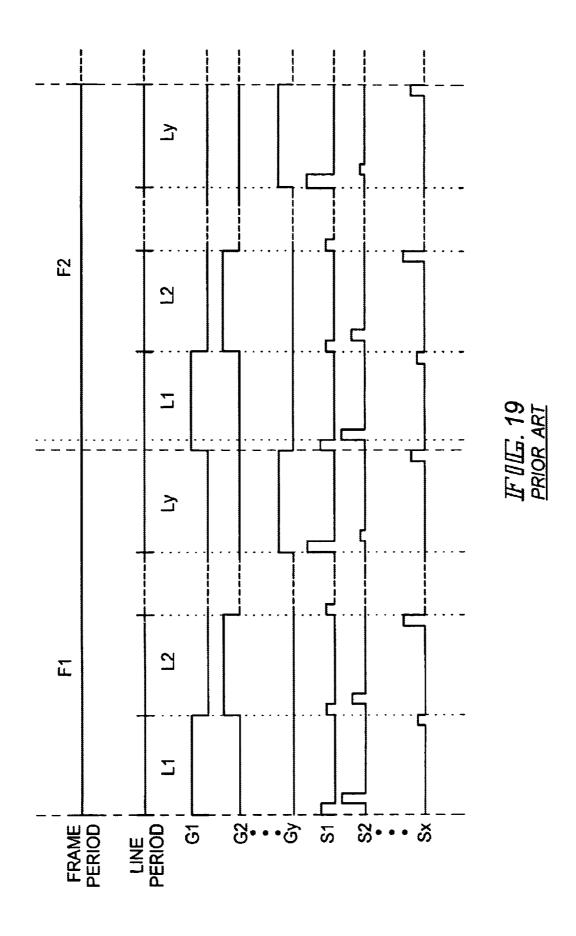

A driving method of the analog system (analog drive) can be cited as a driving method of the EL display device. An explanation regarding the analog drive of the EL display device will be made with references to FIGS. 18 and 19.

FIG. 18 is a diagram showing the structure of a pixel portion 1800 in the EL display device having the analog drive. A gate signal line (G1 to Gy) for inputting a selected signal from a gate signal line driver circuit is connected to a gate electrode of a switching TFT 1801 of the respective pixels. As to a source region and a drain region of the switching TFT 1801 of the respective pixels, one is connected to a source signal line (also called data signal line) (S1 to Sx) for inputting an analog video signal whereas the other is connected to a gate electrode of a driver TFT 1804 and a capacitor 1808 of each of the pixels, respectively.

A source region and a drain region of the driver TFT 1804 of each of the pixels is connected to power supply lines (V1 to Vx), and a drain region thereof is connected to an EL element 1806, respectively. An electric potential of the power supply lines (V1 to Vx) is called a power supply potential. Each of the power supply lines (V1 to Vx) is connected to the capacitor 1808 of the respective pixels.

The EL element 1806 is composed of an anode, a cathode, and an EL layer sandwiched therebetween. When the anode of the EL element 1806 is connected to either the source region or the drain region of the EL driver TFT 1804, the anode and the cathode of the EL element 1806 become a pixel electrode and an opposing electrode, respectively. Alternatively, if the cathode of the EL element 1806 is connected to either the source region or the drain region of the EL driver TFT 1804, then the anode of the EL element 1806 becomes the opposing electrode whereas the cathode thereof becomes the pixel electrode.

It is to be noted that the electric potential of an opposing electrode is herein referred to as opposing potential. It is to be noted that a power supply for giving opposing potential to an opposing electrode is herein referred to as an opposing power supply. The difference between the electric potential of a pixel electrode and the electric potential of an opposing electrode is the EL driving voltage, which is applied to the EL layer.

FIG. 19 is a timing chart illustrating the EL display shown in FIG. 18 when it is being driven by the analog system. A period from the selection of one gate signal line to the selection of a next different gate signal line is called a 1 line period (L). In addition, a period from the display of one image to the display of the next image corresponds to a 1 frame period (F). In the case of the EL display device of FIG.

18, there are y number of the gate signal lines and thus a y number of line periods (L1 to Ly) are provided in 1 frame period.

Because the number of line periods in 1 frame period increases as resolution becomes higher, driver circuits must be driven at a high frequency.

First of all, the power supply lines (V1 to Vx) are held at a constant power supply potential, and the opposing electric potential that is the electric potential of the opposing elec-

trode is also held at a constant electric potential. There is a difference in electric potential between the opposing electric potential and the power supply potential to a degree that the EL element can emit light.

A selected signal from the gate signal line driver circuit is inputted to the gate signal line G1 in the first line period (L1). An analog video signal is then sequentially inputted to source signal lines (S1 to Sx). All the switching TFTs connected to the gate signal line G1 are turned on to thereby input the analog video signal that is inputted to the source signal lines to the gate electrode of the driver TFT through the switching TFT.

The amount of electric current through the channel forming region of a TFT for driving is controlled by its gate voltage.

Here, description is made with regard to, by way of example, a case where the source regions of the TFTs for driving are connected to the power supply lines and the drain regions of the TFTs for driving are connected to the EL elements.

Since the source regions of the TFTs for driving are connected to the power supply lines, the same electric potential is inputted to the respective pixels of the pixel portion. At this point, when an analog signal is inputted to a source signal line, the difference between the electric potential of the signal voltage and the electric potential of the source region of the TFT for driving becomes the gate voltage. The electric current through an EL element depends on the gate voltage of the TFT for driving. Here, the brightness of the emitted light from an EL element is proportional to the electric current between the electrodes of the EL element. In this way, the EL elements emit light under the control of the voltage of analog video signals.

The operation described in the above is repeated. When input of analog video signals to the source signal lines (S1–Sx) is completed, the first line period (L1) ends. It is to be noted that the period until the input of analog video signals to the source signal lines (S1–Sx) is completed combined with a horizontal retrace line period may be a one line period. Then, in the second line period (L2) that follows, a selection signal is inputted to the gate signal line G2. Similarly to the case of the first line period (L1), analog video signals are sequentially inputted to the source signal lines (S1–Sx).

When selection signals are inputted to all the gate signal lines (G1–Gy), all the line periods (L1–Ly) end. When all the line periods (L1–Ly) end, one frame period ends. In one frame period, all the pixels carries out display to form one image. It is to be noted that all the line periods (L1–Ly) combined with a vertical retrace line period may be a one frame period.

As described in the above, the amount of light emitted from an EL element is controlled by an analog video signal, and, by controlling the amount of light emission, gradation 55 display is carried out. This is a so-called analog driving method, where gradation display is carried out by changing the voltage of analog video signals inputted to the source signal lines.

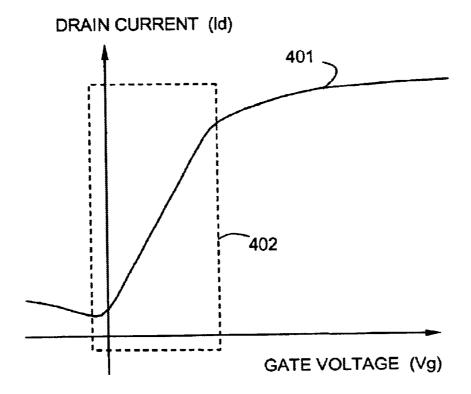

FIG. **20** is a graph illustrating characteristics of a TFT for 60 driving. **401** is referred to as Id-Vg characteristics (or an Id-Vg curve), wherein Id is drain current and Vg is gate voltage. Using this graph, the amount of electric current with regard to arbitrary gate voltage can be known.

In driving an EL element, a region shown by a dotted line 65 **402** of the above Id-Vg characteristics is normally used. The region surrounded by the dotted line **402** is referred to as a

4

saturated region where the drain current Id greatly changes as the gate voltage Vg changes.

In the analog driving method, using the saturated region, the drain current of a TFT for driving is changed by changing its gate voltage.

When a TFT for switching is turned on, an analog video signal inputted from a source signal line to a pixel is applied to a gate electrode of a TFT for driving. In this way, the gate voltage of the TFT for driving is changed. Here, according to the Id-Vg characteristics illustrated in FIG. 20, the drain current with regard to a certain gate voltage is uniquely decided. In this way, predetermined drain current corresponding to the voltage of the analog video signal inputted to the gate electrode of the TFT for driving passes through the EL element, and the EL element emits light the amount of which corresponds to the amount of the electric current.

In this way, the amount of light emitted from the EL element is controlled by an analog video signal, and, by controlling the amount of light emission, gradation display is carried out.

Here, even when the same signal is inputted from the source signal line, the gate voltage of the TFT for driving of each pixel changes if the electric potential of the source region of the TFT for driving changes. Here, the electric potential of the source region of the TFT for driving is given from the power supply line. However, due to potential drop caused by wiring resistance, the electric potential of the power supply line changes depending on its position in the pixel portion.

In addition to the influence of the potential drop caused by wiring resistance of the power supply line in the pixel portion, there is also a problem of potential drop of the connection wiring portion (hereinafter referred to as a power supply line connection wiring portion) from an input portion of the power supply from the external (hereinafter referred to as an external input terminal) to the power supply line of the pixel portion.

More specifically, depending on the length of the wiring from the position of the external input terminal to the position of the power supply line of the pixel portion, the electric potential of the power supply line varies.

Here, this may not present a great problem in such a case where the wiring resistance of the power supply line is small, the display device is relatively small, or the amount of electric current passing through the power supply line is relatively small. Otherwise however, especially when the display device is relatively large, the change in the electric potential of the power supply line due to the wiring resistance becomes large.

In particular, as the display device becomes larger, the variation in the distance from the external input terminal to the power supply line of the pixel portion becomes larger, and the variation in the length of the wiring of the power supply line drawn-around portion becomes larger accordingly. Therefore, the change becomes larger in the electric potential of the power supply line due to the potential drop of the power supply line connection portion.

The variation in the electric potential of the power supply lines due to these factors affects the brightness of the emitted light from the EL elements of the pixels by changing the brightness of the display, and thus, is a cause of uneven display.

A specific example of such variation in the electric potential of the power supply lines is described in the following.

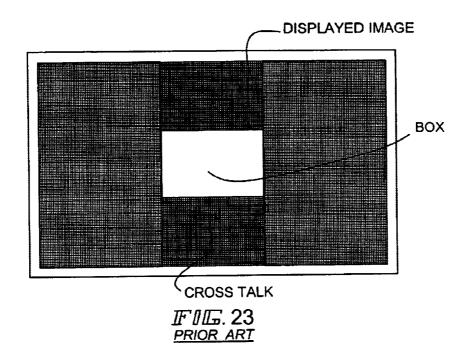

As illustrated in FIG. 23, when a white or black box is displayed on a display, a phenomenon referred to as cross talk arises. This is a phenomenon that difference in the brightness arises over or under the box compared with portions beside the box.

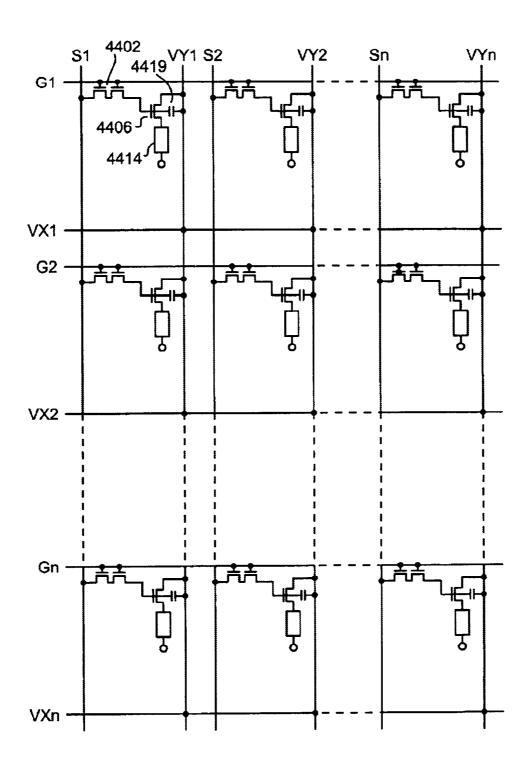

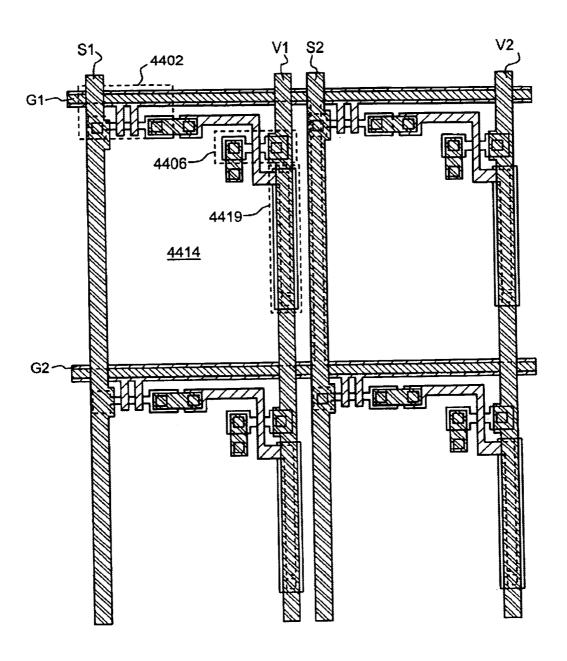

FIGS. 40 and 41 are a partial circuit diagram and a top surface view, respectively, of a pixel portion of a conventional display device where the phenomenon arises.

In FIG. 41, like reference numerals designate like parts in FIG. 40, and the description thereof is omitted.

Each pixel is formed of a TFT 4402 for switching, a TFT 4406 for driving, a storage capacitor 4419, and an EL element 4414.

It is to be noted that, although the TFT 4402 for switching  $_{15}$ is of a double gate structure in FIGS. 40 and 41, it may be of the other structures.

Cross talk arises due to the difference in electric current through the TFT 4406 for driving between each pixel over and under the box and beside the box. The difference arises 20 because the power supply lines V1 and V2 are disposed in parallel with the source signal lines S1 and S2.

For example, as shown in FIG. 23, when a white box is displayed in a part of the display in the power supply line corresponding to the pixel displaying the box, since current 25 flows through the EL element between the source and the drain of the TFT for driving of the pixel displaying the box, the potential drop due to the wiring resistance of the power supply line is greater than that of the power supply line which supplies power only to pixels which do not display the 30 box. Therefore, portions darker than other pixels which do not display the box are generated over and under the box.

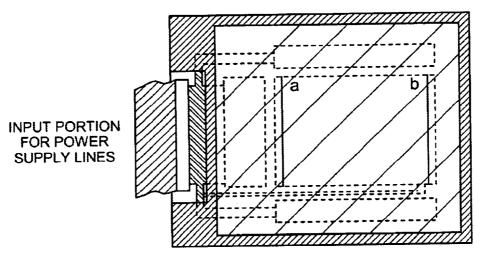

Further, in a conventional active matrix EL display device, as shown in FIG. 24, the power supply line is drawn out from one direction of the display device, and power 35 supply, signals, and the like are inputted from an input

Here, even if the size of the display of the display device is small, no particular problem arises. However, as the size of the display of the display device becomes larger, the  $^{40}$ current consumption increases in proportion to the area of the display.

For example, the current consumption of a display device having a 20-inch display is 25 times as much as that of a display device having a 4-inch display.

Therefore, the potential drop described in the above is a big problem for a display device having a large-sized display.

supply line near the input portion (a in FIG. 24) is not so great, with regard to a power supply line far from the input portion (b in FIG. 24), since the length of the wiring is large, the potential drop caused due to the wiring resistance is large. Therefore, voltage applied to EL elements of pixels 55 plurality of pixels being formed of thin film transistors for having TFTs for driving which are connected to the power supply line (b in FIG. 24) is lowered to deteriorate the quality of the image.

For example, in a 20-inch display device, when the length of the wiring is 700 mm, the width of the wiring is 10 mm, 60 and the sheet resistance is 0.1 ohm, if about 1A of current passes, the potential drop is as much as 10 V, with which normal display is impossible.

#### SUMMARY OF THE INVENTION

The present invention is made in view of the above, and an object of the present invention is to provide an active

matrix EL display device capable of vivid color display with multiple gradations. Another object of the present invention is to provide a high performance electronic apparatus (electronic device) using such an active matrix EL display device.

The present inventor conceived a method of alleviating potential drop due to wiring resistance of a power supply line, in particular, potential drop due to wiring resistance at a portion where the power supply line is drawn out.

Structures according to the present invention are described in the following.

According to the present invention, a display device is provided which comprises a plurality of source signal lines, a plurality of gate signal lines, a plurality of power supply lines, and a plurality of pixels disposed like a matrix, said source signal lines, said gate signal lines, said power supply lines, and said pixels being on an insulating surface, and said plurality of pixels being formed of thin film transistors for switching, thin film transistors for driving, and EL elements,

characterized in that:

said display device has a plurality of drawing-out openings;

said plurality of power supply lines are drawn around to said plurality of drawing-out openings;

electric potential is given to said plurality of power supply lines at said plurality of drawing-out openings; and

said drawing-out openings are provided in at least two directions of said display device.

According to the present invention, a display device is provided which comprises a plurality of source signal lines, a plurality of gate signal lines, a plurality of power supply lines, and a plurality of pixels disposed like a matrix, said source signal lines, said gate signal lines, said power supply lines, and said pixels being on an insulating surface, and said plurality of pixels being formed of thin film transistors for switching, thin film transistors for driving, and EL elements,

characterized in that:

said display device has a drawing-out opening;

said drawing-out opening has a plurality of external input terminals;

five to fifty of said plurality of power supply lines are collected together in one unit and are drawn around to said plurality of external input terminals; and

electric potential is given to said plurality of power supply lines at said plurality of external input terminals.

According to the present invention, a display device is Further, while the potential drop with regard to a power 50 provided which comprises a plurality of source signal lines, a plurality of gate signal lines, a plurality of power supply lines, and a plurality of pixels disposed like a matrix, said source signal lines, said gate signal lines, said power supply lines, and said pixels being on an insulating surface, and said switching, thin film transistors for driving, and EL elements,

characterized in that:

said display device has an external input terminal;

said plurality of power supply lines are drawn around to said external input terminal; and

an electric potential is given to said plurality of power supply lines through said external input terminal by a feedback amplifier in a feedback loop.

A display device may be characterized in that said plu-65 rality of power supply lines are disposed like a matrix.

A display device may be characterized in that said plurality of power supply lines are formed of a wiring layer

forming said source signal lines and a wiring layer forming said gate signal lines.

A display device may be characterized in that said plurality of power supply lines are formed of a wiring layer different from a wiring layer forming said source signal 5 lines, and a wiring layer forming said gate signal lines.

A display device may be characterized in that said plurality of power supply lines are formed of a wiring layer different from a wiring layer forming said gate signal lines, and a wiring layer forming said source signal lines.

A display device may be characterized in that said plurality of power supply lines are formed of a wiring layer different from both a wiring layer forming said gate signal lines and a wiring layer forming said source signal lines.

A display device may be characterized in that the number 15 of said plurality of power supply lines in a column direction is smaller than the number of said plurality of pixels in a column direction.

A display device may be characterized in that the number of said plurality of power supply lines in a row direction is 20 smaller than the number of said plurality of pixels in a row direction.

A display device may be characterized in that a diagonal line of a display portion of said display device is 20 inch or longer.

A personal computer, a telereceiver, a video camera, an image reproduction device, a heat mount display or a portable information terminal may be characterized by applying the display device.

#### BRIEF DESCRIPTION OF THE DRAWINGS

In the accompanying drawings:

- FIG. 1 shows the drawing out openings of the display device of the present invention;

- FIG. 2 shows the circuit structure of the pixel portion of the display device of the present invention;

- FIG. 3 shows the top view of the pixel portion of the display device of the present invention;

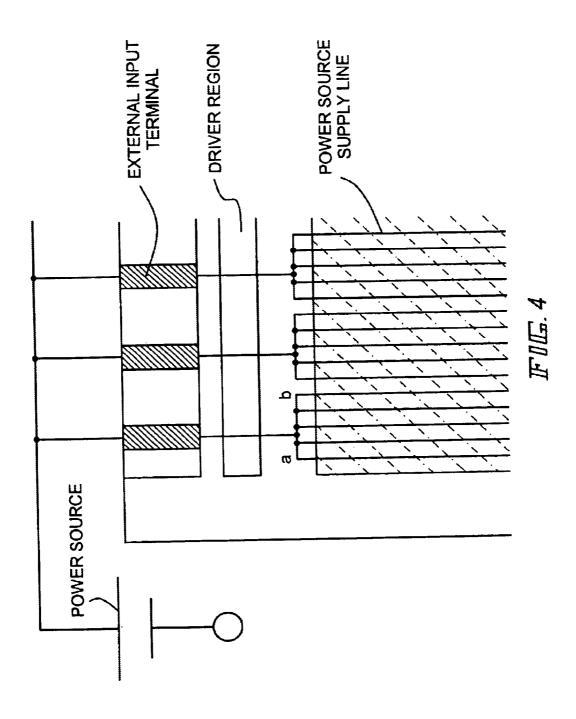

- FIG. 4 shows the shape of the drawing out port of the  $^{40}$  power source supply line of the display device of the present invention;

- FIG. 5 shows the driving method of the display device of the present invention;

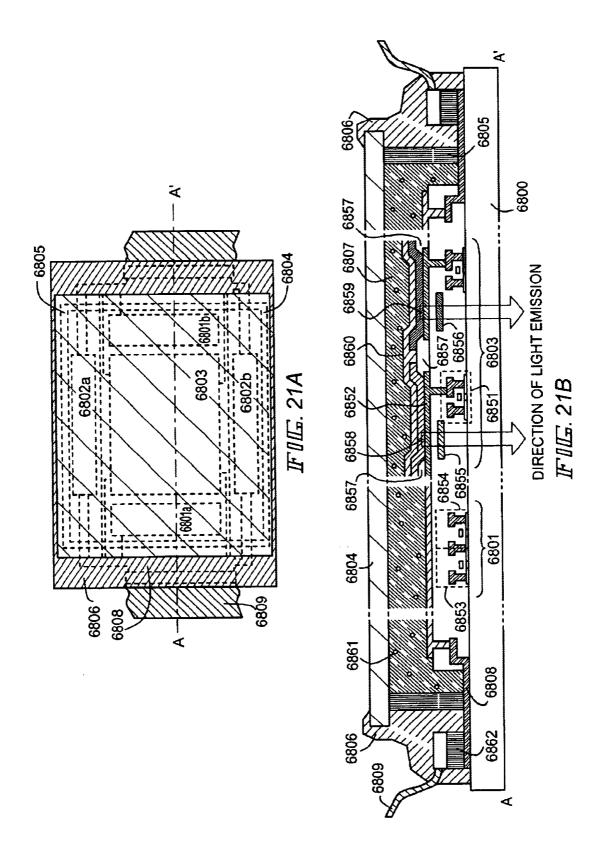

- FIG. 6 shows the top view and the cross section view of the display device of the present invention;

- FIG. 7 shows the top view and the cross section view of the display device of the present invention;

- FIG. 8 shows the cross section view of the display device 50 of the present invention;

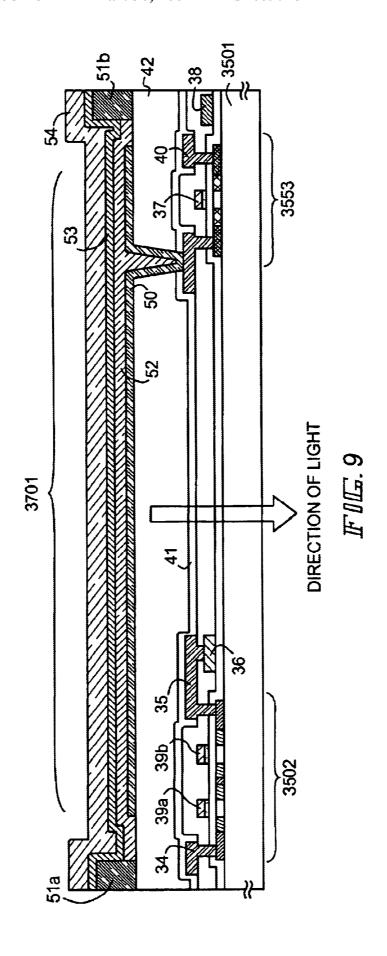

- FIG. 9 shows the cross section view of the display device of the present invention;

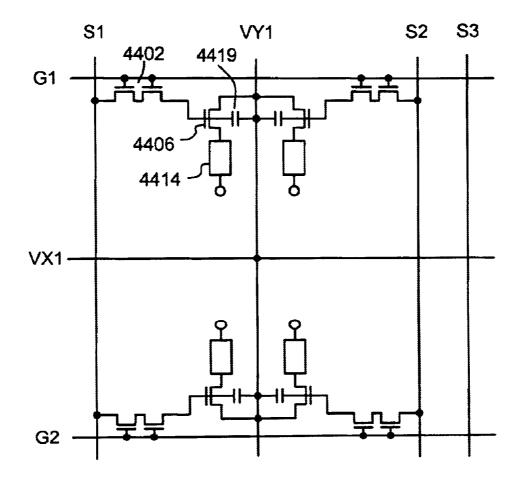

- FIG. 10 shows the circuit diagram of the pixel portion of the display device of the present invention;

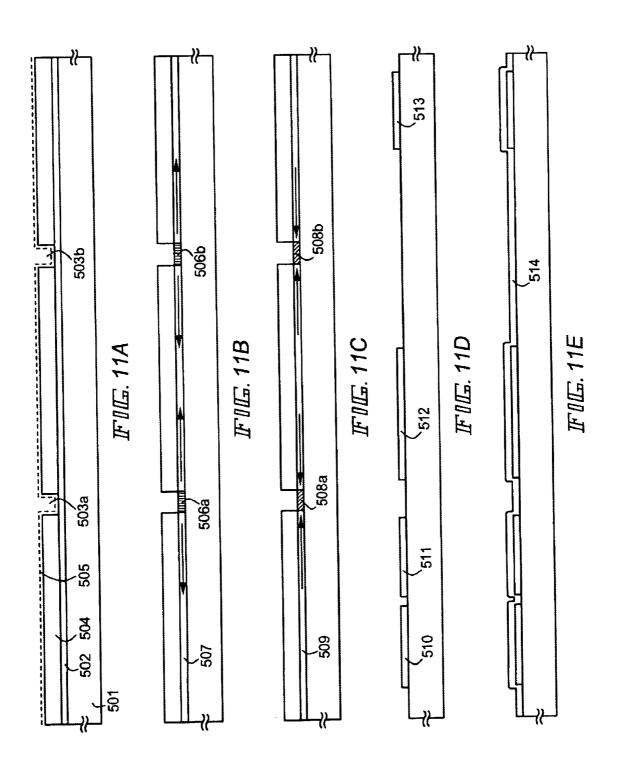

- FIG. 11 shows the manufacturing process of the display device of the present invention;

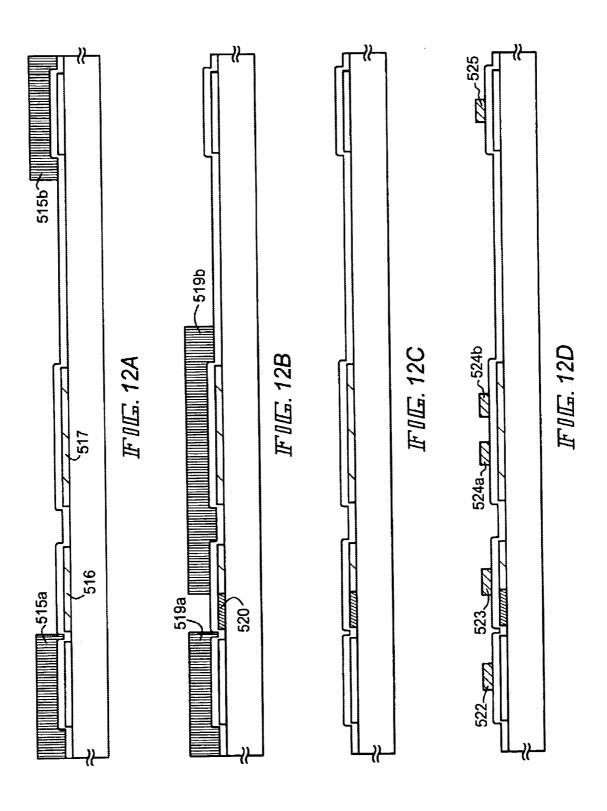

- FIG. 12 shows the manufacturing process of the display device of the present invention;

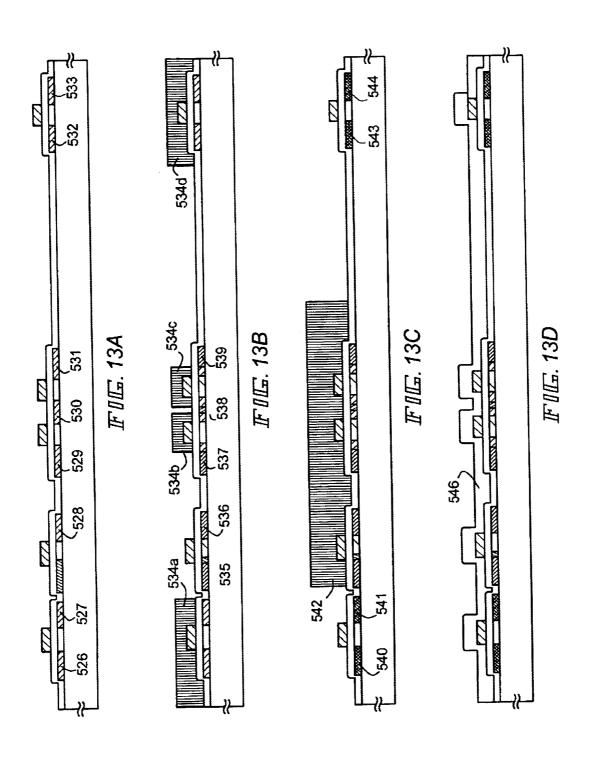

- FIG. 13 shows the manufacturing process of the display device of the present invention;

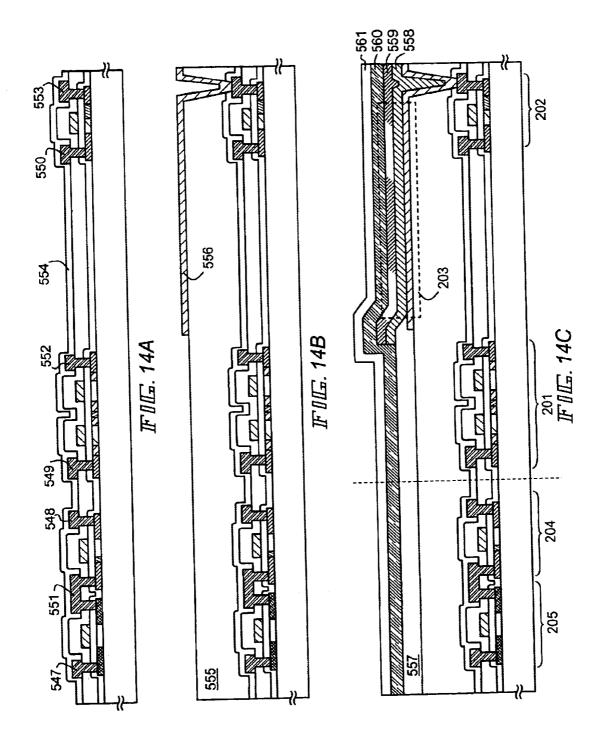

- FIG. 14 shows the manufacturing process of the display device of the present invention;

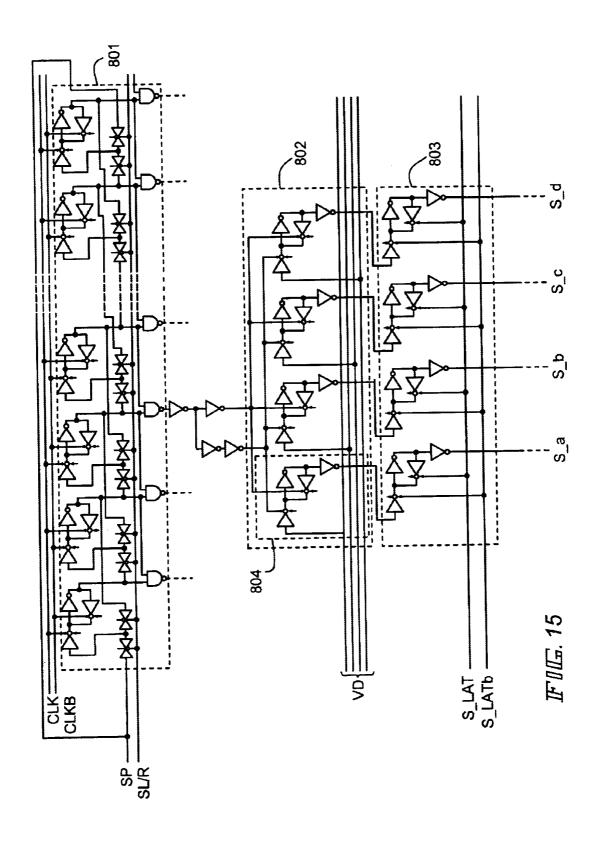

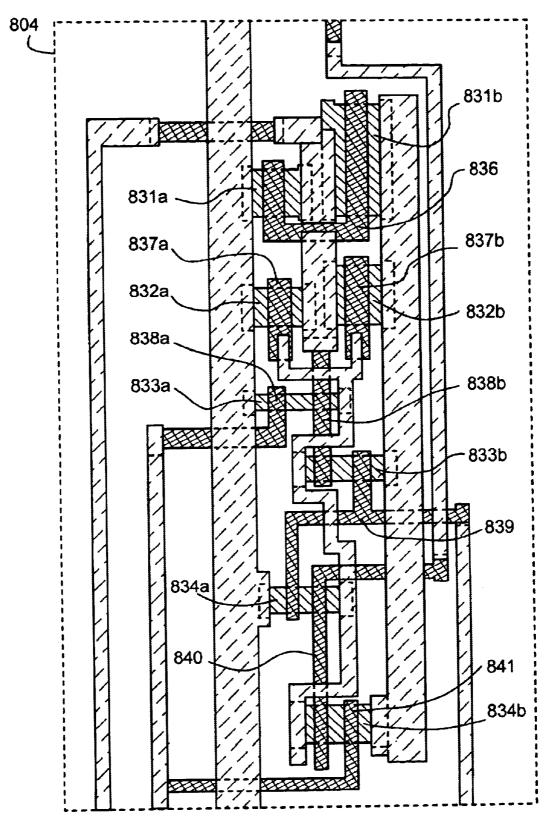

- FIG. 15 shows the circuit diagram of the source signal 65 side driver circuit of the display device of the present invention;

8

- FIG. 16 shows the top view of the latch of the display device of the present invention;

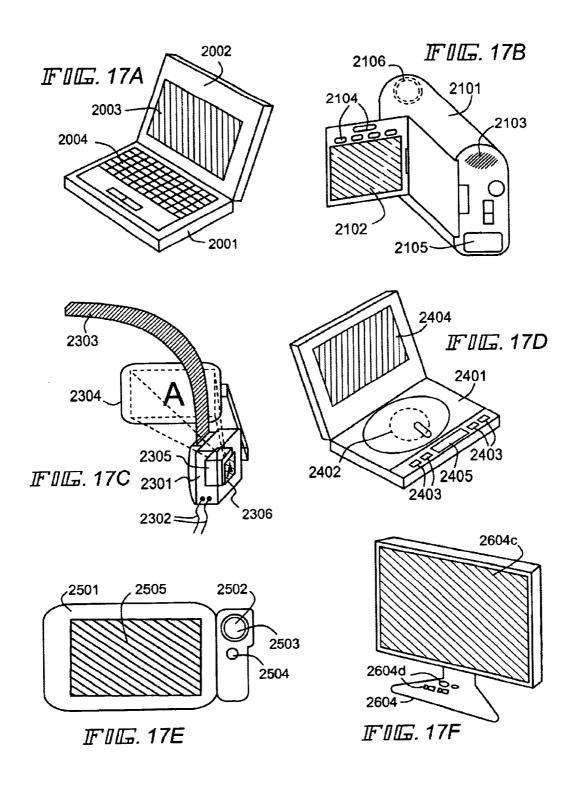

- FIG. 17 shows the electrical appliance using the display device of the present invention;

- FIG. 18 shows the circuit diagram of the pixel portion of the conventional display device;

- FIG. 19 shows the diagram of the timing chart showing the driving method of the display device;

- FIG. 20 shows the diagram of a Id-Vg characteristic of a  $_{10}\,$  TFT;

- FIG. 21 shows the top view and the cross section of the display device of the present invention;

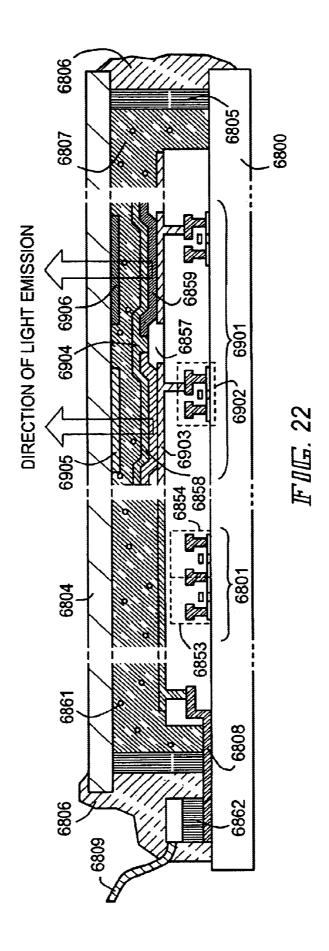

- FIG. 22 shows the cross section of the display device of the present invention;

- FIG. 23 shows an example of the generation of cross talk;

- FIG. 24 shows the diagram of a drawing out port of the display device of the present invention;

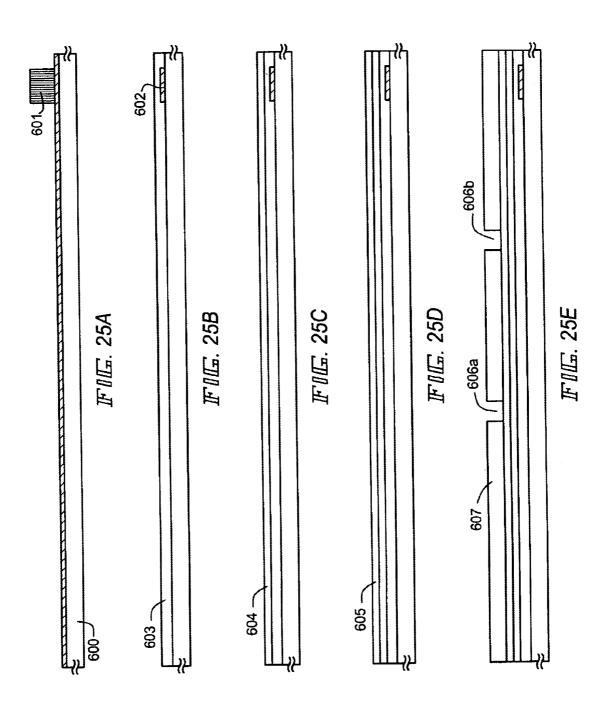

- FIG. 25 shows the manufacturing process of the display device of the present invention;

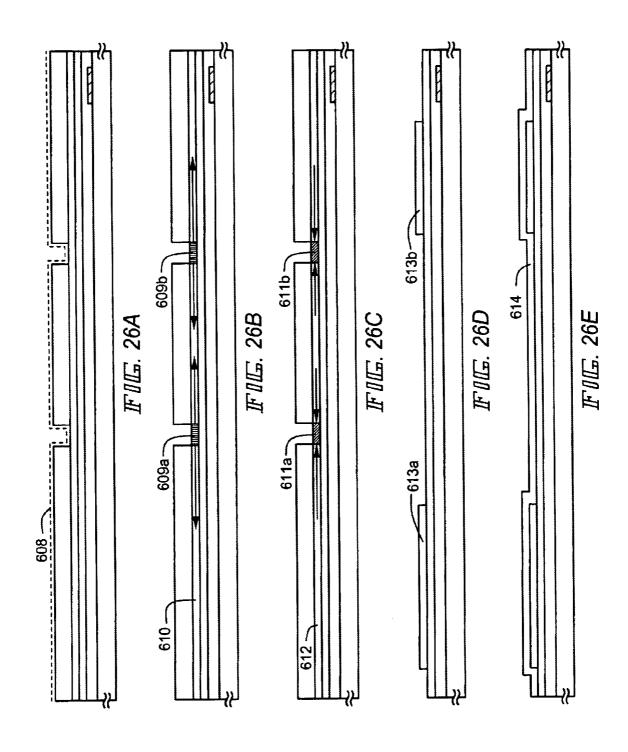

- FIG. 26 shows the manufacturing process of the display device of the present invention;

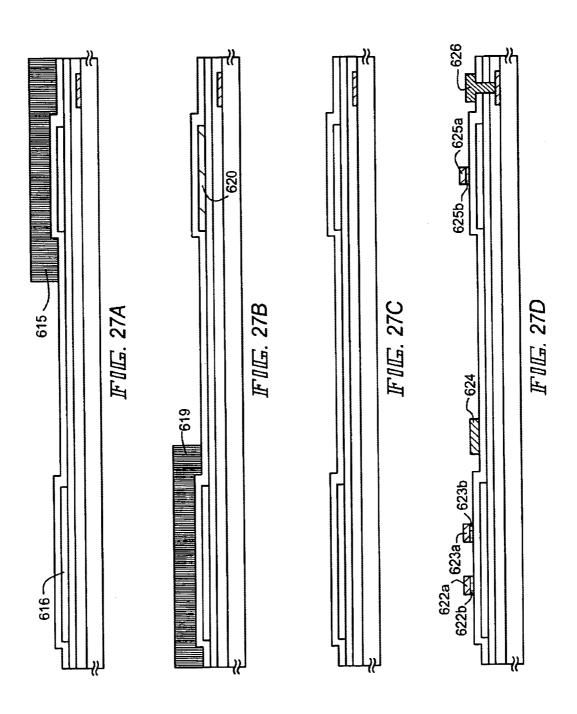

- FIG. 27 shows the manufacturing process of the display device of the present invention;

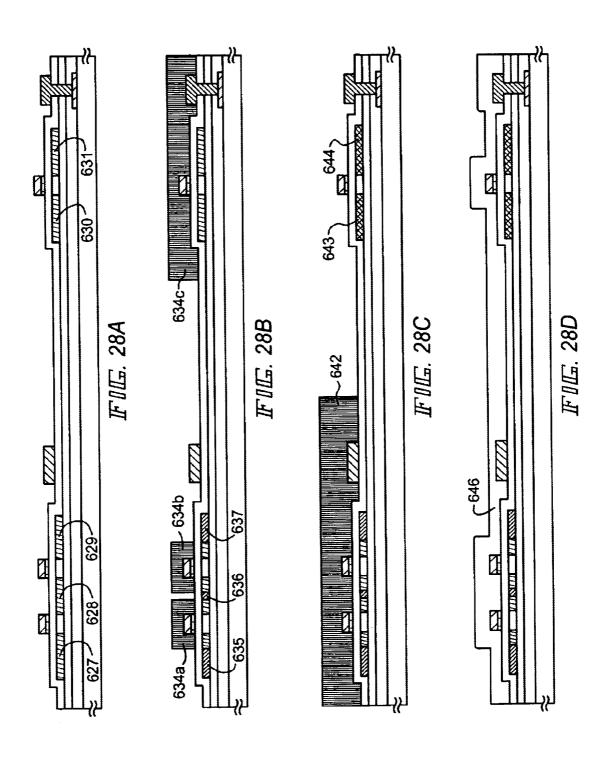

- FIG. 28 shows the manufacturing process of the display device of the present invention;

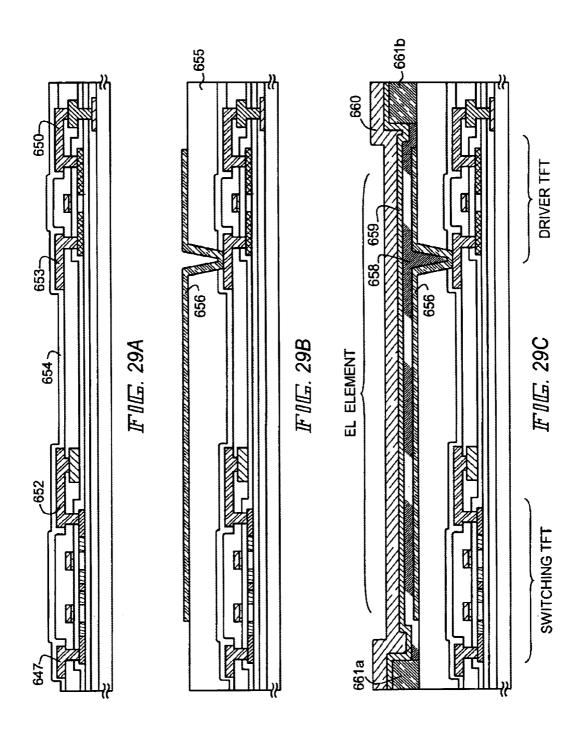

- FIG. 29 shows the manufacturing process of the display device of the present invention;

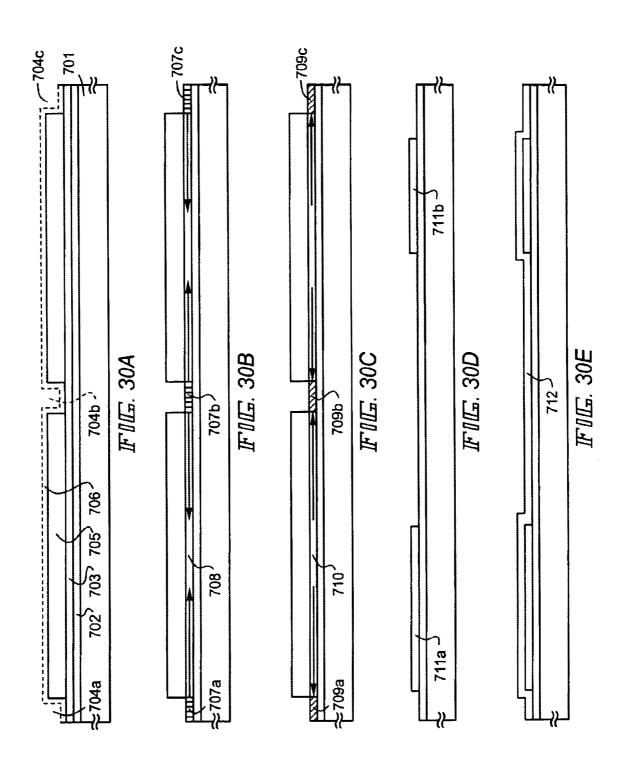

- FIG. 30 shows the manufacturing process of the display  $_{30}$  device of the present invention;

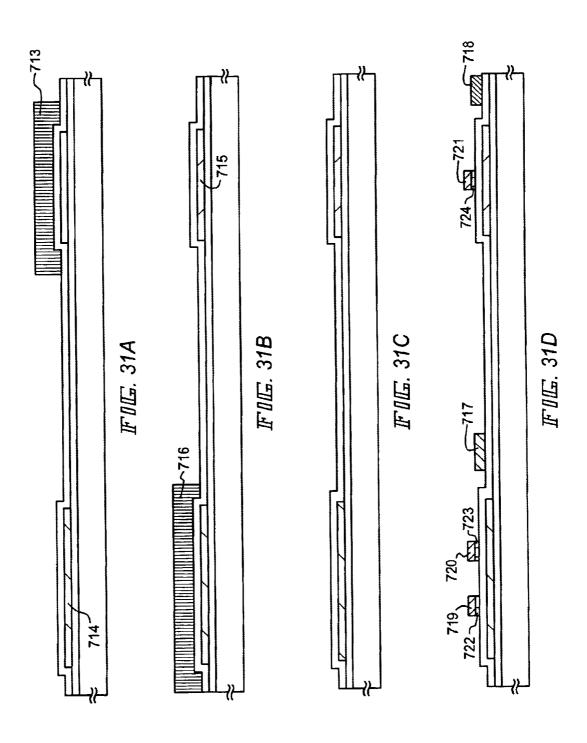

- FIG. 31 shows the manufacturing process of the display device of the present invention;

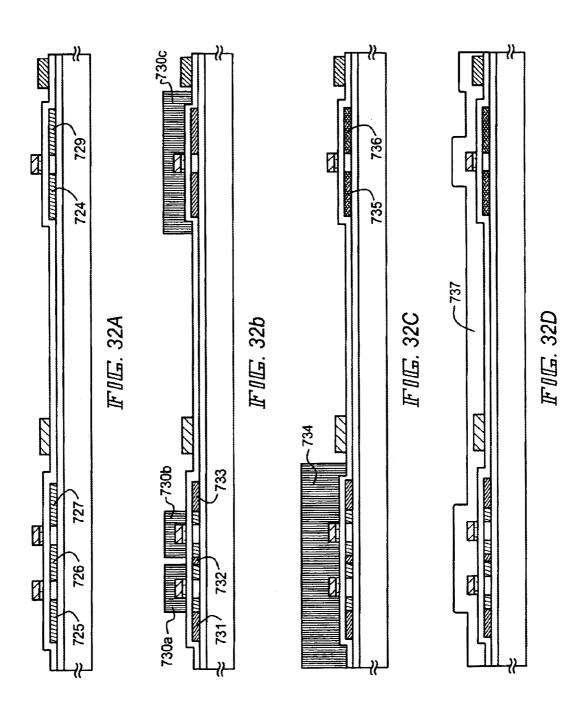

- FIG. 32 shows the manufacturing process of the display device of the present invention;

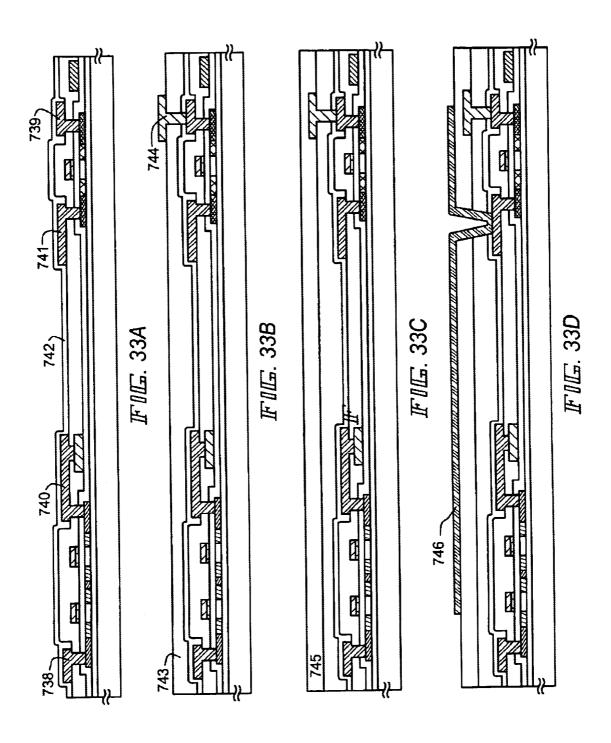

- FIG. 33 shows the manufacturing process of the display device of the present invention;

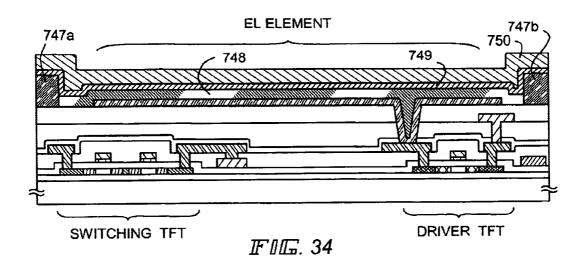

- FIG. 34 shows the manufacturing process of the display device of the present invention;

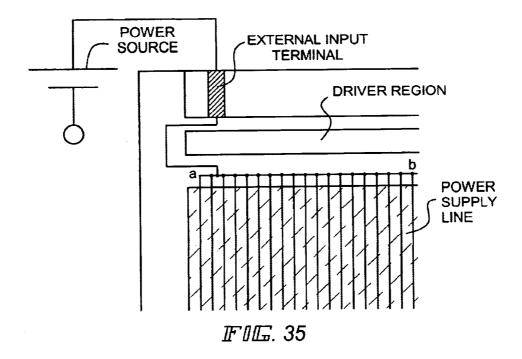

- FIG. 35 shows the shape of the drawing out port of the power source supply line of the conventional display device of the present invention;

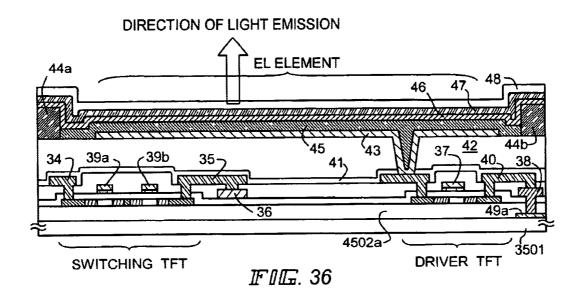

- FIG. 36 shows the cross section view of the display device of the present invention:

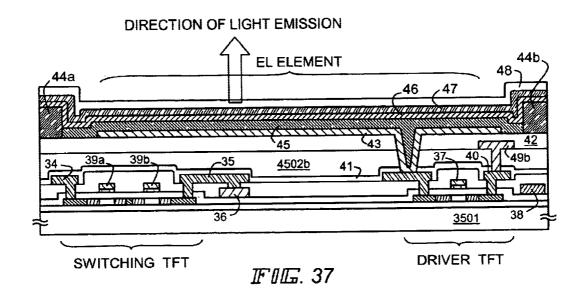

- FIG. 37 shows the cross section view of the display device of the present invention;

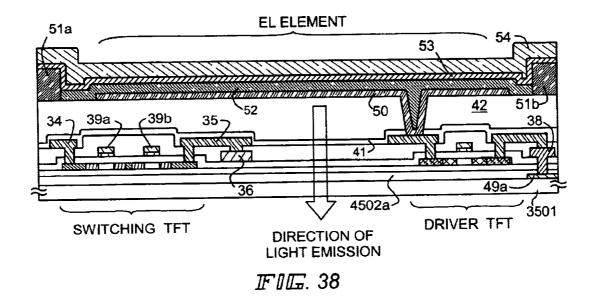

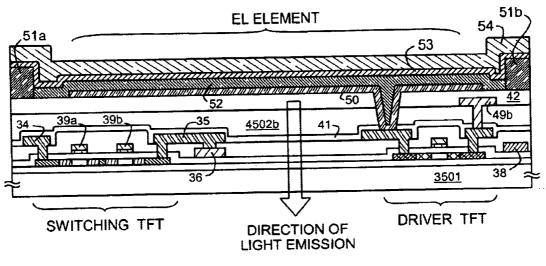

- FIG. 38 shows the cross section view of the display device of the present invention;

- FIG. 39 shows the cross section view of the display device of the present invention;

- FIG. 40 shows the circuit diagram of the pixel portion of the conventional display device;

- FIG. 41 shows the top view of the pixel portion of the conventional display device;

- FIG. 42 shows the top view of the pixel portion of the display device of the present invention;

- FIG. 43 shows the circuit diagram of the pixel portion of the display device of the present invention;

- FIG. 44 shows the top view of the pixel portion of the display device of the present invention; and

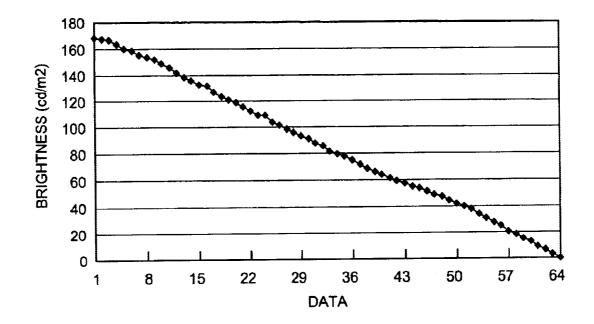

- FIG. **45** is a diagram showing the gray-scale characteristics of the display device of the present invention.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Structures of display devices according to the present invention are now described in the following.

(Embodiment Mode 1)

Power supply lines of a pixel portion is drawn out to the external not in one direction but in a plurality of directions.

Embodiment Mode 1 is described with reference to FIG.

As illustrated in FIG. 1, the power supply lines are drawn out in two directions, i.e., from a power supply line input portion 1 and a power supply line input portion 2.

An input portion as used herein shall mean a portion formed of a plurality of external input terminals and through 10 which power supply potential, picture signals, and the like are inputted from the external to the display device.

By drawing out the power supply lines in two directions of the display device in this way, compared with a case where the power supply lines are drawn out in one direction, 15 the length of the wiring from the power supply lines of the pixel portion to the external input terminals can be shorter and the variation in the length of the wiring can be decreased.

By the above structure, the influence of the potential drop 20 at the drawn-around portion of the power supply lines around the pixel portion can be decreased.

(Embodiment Mode 2)

In the present embodiment mode, a small number of wirings of an input portion of power supply lines are 25 collected together in a unit and the respective units are drawn out to a plurality of external input terminals which are not next to each other and which are at respective input portions.

A structure of the present embodiment mode is illustrated 30 in FIG. 4

In the present embodiment mode, compared with a case where all the power supply lines of a pixel portion are collected together in one unit to be drawn out to one external input terminal, the length of the wiring from the respective 35 collected power supply lines to the external input terminals can be shorter and the variation in the length of the wiring can be decreased.

More specifically, the difference in length between wirings a and b in FIG. 4 is greatly decreased compared with the difference in length between wirings a and b in FIG. 35.

By the above structure, the influence of the potential drop at the drawn-around portion of the power supply lines around the pixel portion can be decreased. (Embodiment Mode 3)

As described in the above, the amount of electric current through power supply lines can be large in a large-sized display device. In such a case, the influence of potential drop due to wiring resistance between a pixel region and external input terminals is not negligible.

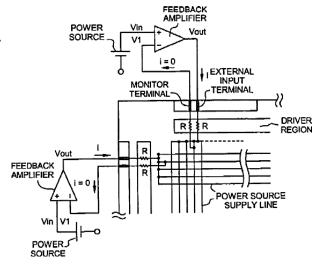

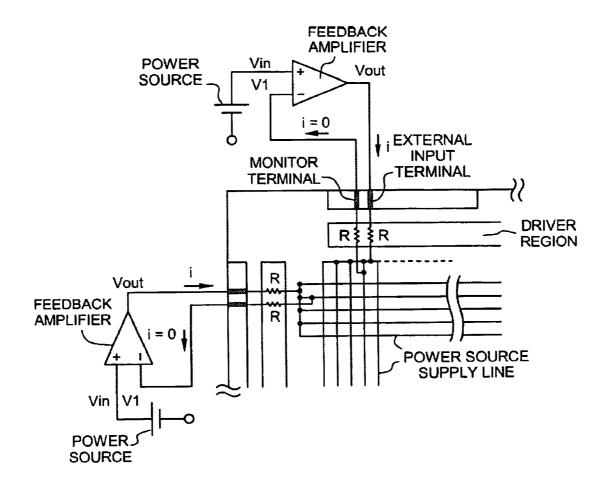

One countermeasure for this would be increasing in advance the potential of an external power supply. However, since electric current through the power supply lines changes depending on what is displayed, it is not desirable to uniformly increase the potential of the external power 55 supply. Therefore, in the present embodiment mode, it is proposed to use a feedback amplifier and to include wiring causing potential drop in a feedback loop.

As illustrated in FIG. 5, an external input terminal is connected to an output of a feedback amplifier. Voltage to be applied to power supply lines is inputted to a noninverting input terminal (+) of a feedback amplifier. Electric potential of the power supply lines of the pixel portion is monitored and is applied to an inverting input terminal (-). According to the principle of the feedback amplifier, the noninverting input terminal and the inverting input terminal are operated to be at the same electric potential, and thus, electric

10

potential higher by the potential drop is outputted from an output terminal of the feedback amplifier. As described in the above, potential compensation is carried out to cancel the gap in the electric potential.

When the wiring resistance of the power supply line input portion is R and the electric current is i, potential drop of Ri arises. However, at the monitor terminal, since almost no electric current passes through the monitor terminal, no potential drop arises.

Note that the feedback amplifier comprising an external IC is formed over an external substrate after forming a panel having the pixel region.

(Embodiment Mode 4)

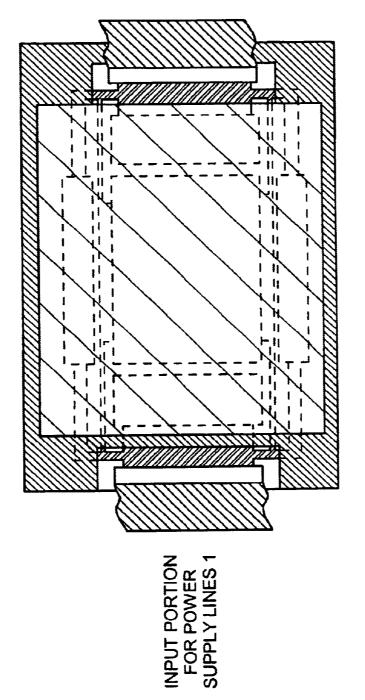

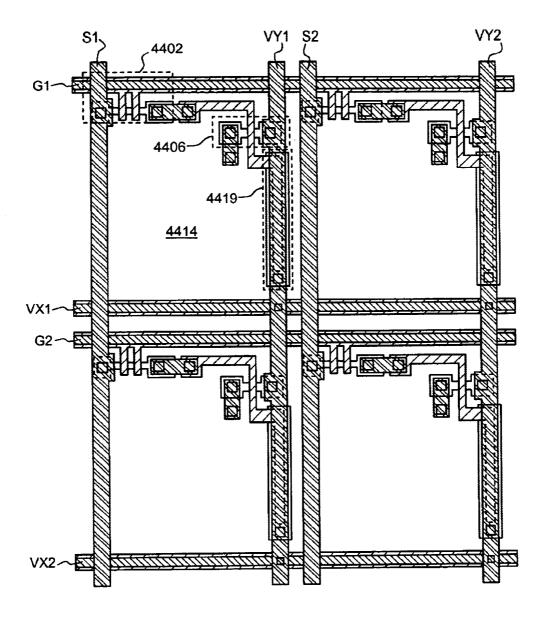

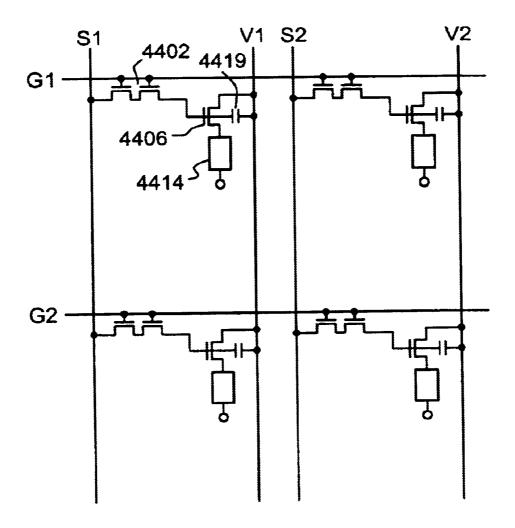

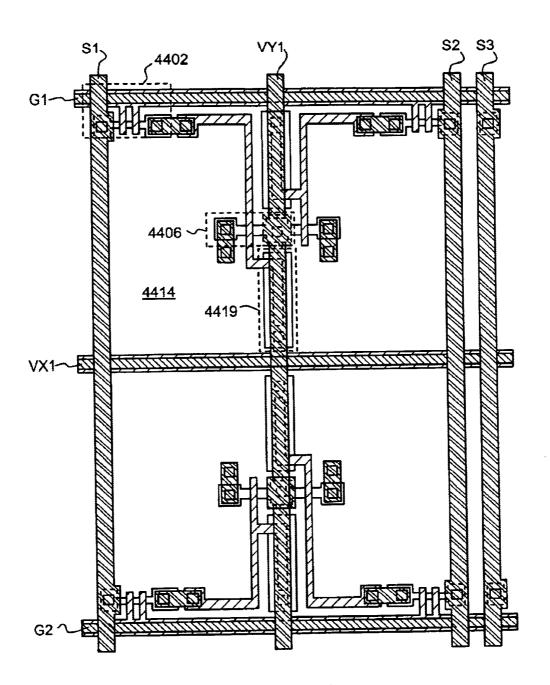

FIG. 2 is a circuit diagram illustrating a structure of a pixel portion according to the present invention.

Each pixel of the pixel portion is formed of a TFT 4402 for switching, a TFT 4406 for driving, a storage capacitor 4419, and an EL element 4414. Power supply lines (VX1–VXn and VY1–VYn) are disposed not only in a direction in parallel with source signal lines (S1–Sn) but also in a direction perpendicular to them. Therefore, voltage is supplied to either a source region or a drain region of the TFT 4406 for driving of the pixel from the respective directions. Since electric current through the EL element 4414 is supplied not only from the direction in parallel with the source signal lines S1–Sn but from the direction perpendicular to them, occurrence of conventional cross talk can be suppressed.

Here, the power supply lines are shared between pixels next to each other. This can decrease the area occupied by the power supply lines in the respective pixels. Therefore, the opening ratio can be improved even with regard to a pixel having a structure where power supply lines are disposed both vertically and horizontally (like a matrix).

Embodiment Modes 1 to 4 can be freely combined with each other to be implemented. (Embodiments)

Embodiments of the present invention are described in the following.

0 (Embodiment 1)

45

FIG. 4 illustrates an example where a small number of power supply lines are collected together in one unit and are connected to an external input terminal, which is described in Embodiment 2.

Since the potential drop becomes larger as the size of the display becomes larger, it is necessary to make the wirings as short as possible which draw out the power supply lines. According to the present invention, a small number of power supply lines are collected together in one unit, and are outputted to an adjacent external input terminal.

In the example illustrated in FIG. 4, a small number of power supply lines are collected together in one unit, and are connected to an external input terminal through a driver region. In this way, the wiring resistance is decreased.

It is desirable that about five to fifty power supply lines are collected together in one unit.

(Embodiment 2)

FIG. 3 is a top view of a part (four pixels) of the pixel portion of the circuit diagram illustrated in FIG. 2 as an embodiment of the present invention.

It is to be noted that like reference numerals designate like parts in FIG. 2.

Each pixel is formed of a TFT 4402 for switching, a TFT 4406 for driving, a capacitor 4419, and an EL element 4414. In this embodiment, power supply lines VX1 and VX2 are disposed in parallel with gate signal lines G1 and G2 using a wiring material similar to that of the gate signal lines G1

and G2. The power supply lines VX1 and VX2 are connected through contact holes to conventional power supply lines VY1 and VY2 in parallel with the source signal lines S1 and S2.

A structure where power supply lines in parallel with the gate signal lines are formed using a wiring layer forming the gate signal lines as the present embodiment is herein referred to as Embodiment 1 of a pixel structure according to the present invention.

In Embodiment 1 of the pixel structure according to the present invention, compared with a conventional case where the pixels illustrated in FIGS. 40 and 41 are actually formed, matrix-like power supply lines can be formed without increasing the number of masks.

The present embodiment can be freely combined with Embodiment 1 to be implemented. (Embodiment 3)

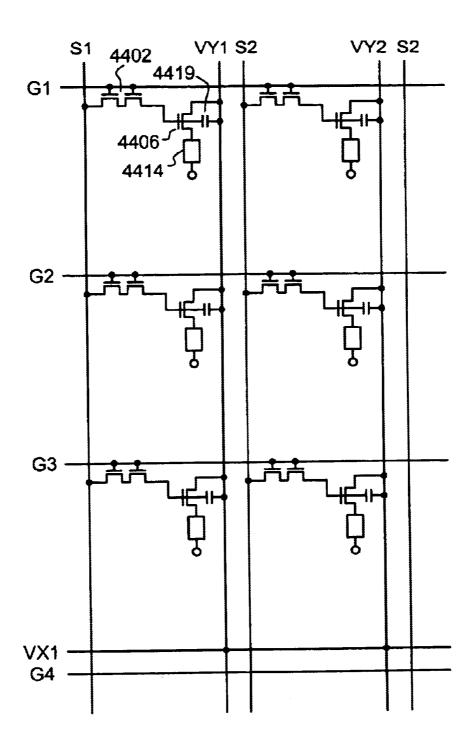

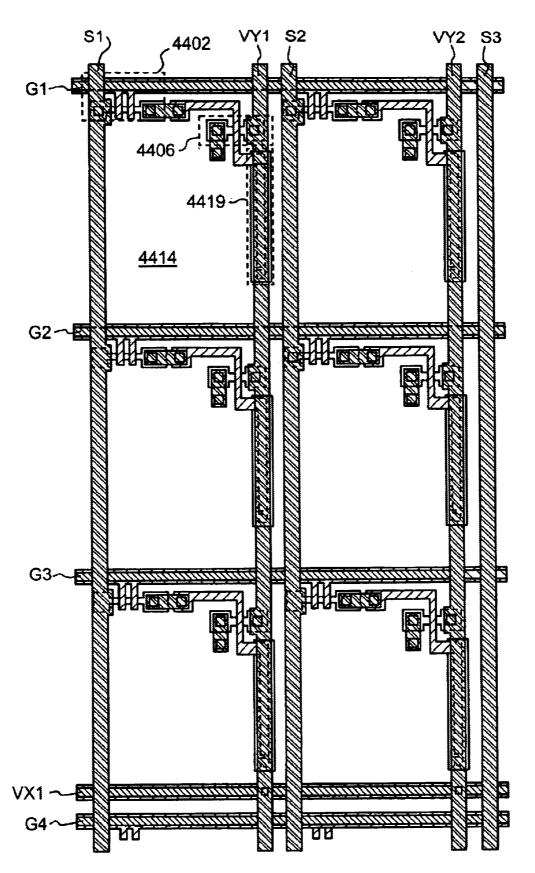

In the present embodiment, a case where power supply lines are shared between pixels next to each other described in Embodiment 4 is described with reference to FIGS. 10 and 42–44.

It is to be noted that, in the present embodiment, G1-G4 are gate wirings (a part of gate signal lines) of a TFT 4402 for switching, S1-S3 are source wirings (a part of source signal lines) of the TFT 4402 for switching, 4406 is a TFT for driving, 4414 is an EL element, VY1-VY2 are power supply lines in parallel with the source wirings, VX1-VX2 are power supply lines in parallel with the gate wirings, and 4419 is a storage capacitor.

FIG. 10 illustrates a case where the power supply lines VY1 and VX1 are shared between two pixels next to each other. It is characteristic that the two pixels are formed so as to be symmetrical with respect to the power supply lines VY1 and VX1. In this case, since the number of the power supply lines can be decreased, the aperture ratio of the display device can be improved and the pixel portion can be made highly precise.

FIG. 42 is a top view of FIG. 10. It is to be noted that like reference numerals designate like parts in FIG. 10, and the description thereof is omitted.

FIG. 43 illustrates another embodiment of the present invention. In the present Embodiment, power supply lines in 40 an X direction are not disposed with regard to all pixel rows, and are 1/n of the number of the pixel rows, wherein n is a natural number which is 2 or larger. Here, a case where n=3 is illustrated.

FIG. 44 is a top view of FIG. 43. It is to be noted that like 45 reference numerals designate like parts in FIG. 43, and the description thereof is omitted.

The present embodiment can be freely combined with Embodiments 1 and 2 to be implemented. (Embodiment 4)

Though, according to the present invention, both n-channel type TFTs and p-channel type TFTs can be used as TFTs for driving of pixels, in case anodes of EL elements are pixel electrodes while their cathodes are opposing electrodes, it is preferable that the TFTs for driving are 55 p-channel type TFTs. On the contrary, in case the anodes of the EL elements are the opposing electrodes while their cathodes are the pixel electrodes, it is preferable that the TFTs for driving are n-channel type TFTs.

The present embodiment can be freely combined with 60 Embodiments 1 to 3 to be implemented. (Embodiment 5)

An example of manufacturing an EL display device of the present invention is explained in this embodiment.

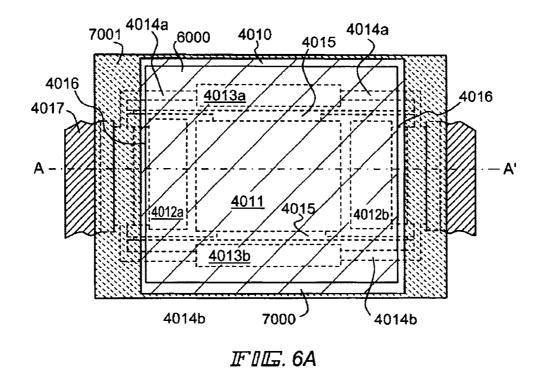

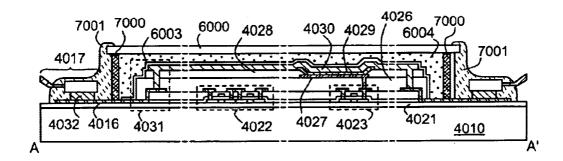

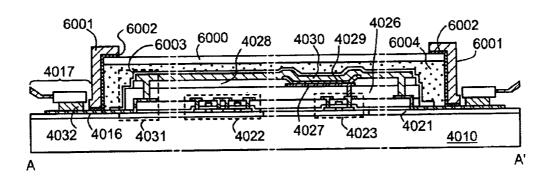

FIG. **6A** is a top view of an EL display device using the 65 present invention. FIG. **6B** shows a cross sectional view which is cut along the line **A–A'** in FIG. **6A**

12

In FIG. 6A, reference numeral 4010 is a substrate, reference numeral 4011 is a pixel portion, reference numerals 4012a and 4012b are source signal line driver circuits, and reference numerals 4013a and 4013b are gate signal line driver circuits. Each driver circuit is connected to external equipment, through an FPC 4017, via wirings 4014a, 4014b, 4015 and 4016.

A cover member 6000, a sealing material (also referred to as a housing material) 7000, and an airtight material (a second sealing material) 7001 are formed so as to enclose at least the pixel portion 4011, preferably the driver circuits 4012a, 4012b, 4013a, and 4013b and the pixel portion 4011, at this point.

Further, FIG. 6B is a cross sectional structure of the EL display device of the Embodiment 5. A driver circuit TFT 4022 (note that a CMOS circuit in which an n-channel TFT and a p-channel TFT are combined is shown in the figure here), a pixel portion TFT 4023 (note that only a driver TFT for controlling the current flowing to an EL element is shown here) are formed on a base film 4021 on a substrate 4010. The TFTs may be formed using a known structure (a top gate structure or a bottom gate structure).

After the driver circuit TFT 4022 and the pixel portion TFT 4023 are completed, a pixel electrode 4027 is formed on an interlayer insulating film (leveling film) 4026 made from a resin material. The pixel electrode 4027 is formed from a transparent conductive film for electrically connecting to a drain of the pixel TFT 4023. An indium oxide and tin oxide compound (referred to as ITO) or an indium oxide and zinc oxide compound can be used as the transparent conductive film. An insulating film 4028 is formed after forming the pixel electrode 4027, and an open portion is formed on the pixel electrode 4027.

An EL layer 4029 is formed next. The EL layer 4029 may be formed having a lamination structure, or a single layer structure, by freely combining known EL materials (such as a hole injecting layer, a hole transporting layer, a light emitting layer, an electron transporting layer, and an electron injecting layer). A known technique may be used to determine which structure to use. Further, EL materials exist as low molecular weight materials and high molecular weight (polymer) materials. Evaporation is used when using a low molecular weight material, but it is possible to use easy methods such as spin coating, printing, and ink jet printing when a high molecular weight material is employed.

In this embodiment, the EL layer is formed by evaporation using a shadow mask. Color display becomes possible by forming emitting layers (a red color emitting layer, a green color emitting layer, and a blue color emitting layer), capable of emitting light having different wavelengths, for each pixel using a shadow mask. In addition, methods such as a method of combining a charge coupled layer (CCM) and color filters, and a method of combining a white color light emitting layer and color filters may also be used. Of course, the EL display device can also be made to emit a single color of light.

After forming the EL layer 4029, a cathode 4030 is formed on the EL layer. It is preferable to remove as much as possible any moisture or oxygen existing in the interface between the cathode 4030 and the EL layer 4029. It is therefore necessary to use a method of continuously depositing the EL layer 4029 and the cathode 4030 in vacuum, or a method of depositing the EL layer 4029 in an inert gas atmosphere and depositing the cathode 4030 without exposure to the atmosphere. The above film deposition becomes possible in this embodiment by using a multi-chamber method (cluster tool method) film deposition apparatus.

Note that a lamination structure of a LiF (lithium fluoride) film and an Al (aluminum) film is used in this embodiment as the cathode 4030. Specifically, a 1 nm thick LiF (lithium fluoride) film is formed by evaporation on the EL layer 4029, and a 300 nm thick aluminum film is formed on the LiF film. An MgAg electrode which is a known cathode material, may of course also be used. The wiring 4016 is then connected to the cathode 4030 in a region denoted by reference numeral 4031. The wiring 4016 is an electric power supply line for imparting a predetermined voltage to the cathode 4030, and 10 is connected to the FPC 4017 through a conducting paste material 4032.

In order to electrically connect the cathode 4030 and the wiring 4016 in the region denoted by reference numeral 4031, it is necessary to form a contact hole in the interlayer 15 insulating film 4026 and the insulating film 4028. The contact holes may be formed at the time of etching the interlayer insulating film 4026 (when forming a contact hole for the pixel electrode) and at the time of etching the insulating film 4028 (when forming the opening portion 20 before forming the EL layer). Further, when etching the insulating film 4028, etching may be performed all the way to the interlayer insulating film 4026 at one time. A good contact hole can be formed in this case, provided that the interlayer insulating film 4026 and the insulating film 4028 25 are the same resin material.

A passivation film 6003, a filler material 6004, and the cover member 6000 are formed covering the surface of the EL element thus made.

In addition, the sealing material 7000 is formed between 30 the cover member 6000 and the substrate 4010, so as to surround the EL element portion, and the airtight material (the second sealing material) 7001 is formed on the outside of the sealing material 7000.

bonding the cover member 6000 at this point. PVC (polyvinyl chloride), epoxy resin, silicone resin, PVB (polyvinyl butyral), and EVA (ethylene vinyl acetate) can be used as the filler material 6004. If a drying agent is formed on the inside of the filler material 6004, then it can continue to maintain a moisture absorbing effect, which is preferable.

Further, spacers may be contained within the filler material 6004. The spacers may be a powdered substance such as BaO, giving the spacers themselves the ability to absorb moisture.

When using spacers, the passivation film 6003 can relieve the spacer pressure. Further, a film such as a resin film can be formed separately from the passivation film to relieve the spacer pressure.

Furthermore, a glass plate, an aluminum plate, a stainless 50 steel plate, an FRP (fiberglass-reinforced plastics) plate, a PVF (polyvinyl fluoride) film, a Mylar film, a polyester film, and an acrylic film can be used as the cover member 6000. Note that if PVB or EVA is used as the filler material 6004, it is preferable to use a sheet with a structure in which several tens of  $\mu$ m of aluminum foil is sandwiched by a PVF film or a Mylar film.

However, depending upon the light emission direction from the EL element (the light radiation direction), it is necessary for the cover member 6000 to have light trans- 60 mitting characteristics.

Further, the wiring 4016 is electrically connected to the FPC 4017 through a gap between the sealing material 7000, the airtight material 7001 and the substrate 4010. Note that although an explanation of the wiring 4016 has been made here, the wirings 4014a, 4014b and 4015 are also electrically connected to the FPC 4017 by similarly passing underneath

the sealing material 7000, the airtight material 7001 and the substrate 4010.

In this embodiment, the cover member 6000 is bonded after forming the filler material 6004, and the sealing material 7000 is attached so as to cover the lateral surfaces (exposed surfaces) of the filler material 6004, but the filler material 6004 may also be formed after attaching the cover member 6000 and the sealing material 7000. In this case, a filler material injection opening is formed through a gap formed by the substrate 4010, the cover member 6000, and the sealing material 7000. The gap is set into a vacuum state (a pressure equal to or less than 10<sup>-2</sup> Torr), and after immersing the injection opening in the tank holding the filler material, the air pressure outside of the gap is made higher than the air pressure within the gap, and the filler material fills the gap.

The present embodiment can be freely combined with Embodiments 1 to 4 to be implemented. (Embodiment 6)

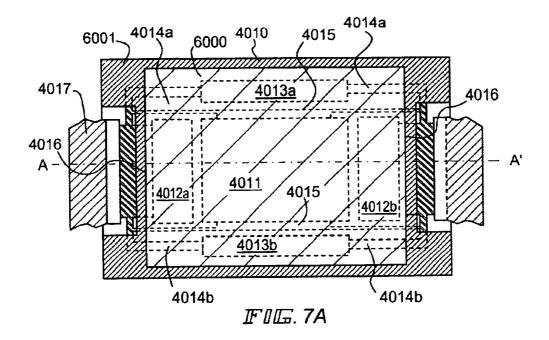

An example of an EL display device in accordance with the present invention, manufactured in a form different from that of Embodiment 5 according to the present invention, will be described with reference to FIGS. 7A and 7B. It is to be noted that like reference numerals designate like parts in FIGS. 6A and 6B, and the description thereof is omitted.

FIG. 7A is a top view of the EL display device of Embodiment 6, and FIG. 7B is a cross-sectional view taken along the line A-A' in FIG. 7A.

In accordance with Embodiment 5, a passivation film 6003 is formed by covering the surface of an EL element.

Further, a filler material 6004 is provided so as to cover the EL element. The filler material 6004 also functions as an adhesive for bonding a cover member 6000. As the filler material 6004, polyvinyl chloride (PVC), epoxy resin, silicone resin, polyvinyl butyral (PVB) or ethylene-vinyl The filler material 6004 functions as an adhesive for 35 acetate (EVA) may be used. Preferably, a desiccant is provided in the filler material 6004 to maintain a moisture absorbing effect.

> The filler material 6004 may also contain a spacer. The spacer may be particles of BaO or the like such that the spacer itself has a moisture absorbing effect.

> If a spacer is provided, the passivation film 6003 can reduce the influence of the spacer pressure. A resin film or the like may also be provided independently of the passivation film to reduce the influence of the spacer pressure.

> As the cover member 6000, a glass sheet, an aluminum sheet, a stainless steel sheet, a fiberglass-reinforced plastics (FRP) sheet, polyvinyl fluoride (PVF) film, Mylar film, polyester film, acrylic film, or the like may be used. If PVB or EVA is used as the filler material 6004, it is preferable to use a sheet having a structure in which an aluminum foil having a thickness of several tens of  $\mu m$  is sandwiched between PVF films or Mylar films.

> Some setting of the direction of luminescence from the EL element (the direction of light emission) necessitates making the cover member 6000 transparent.

Next, the cover member 6000 is bonded by using the filler material 6004. Thereafter, a frame member 6001 is attached so as to cover side surfaces (exposed surfaces) formed by the filler material 6004. The frame member 6001 is bonded by a sealing material 6002 (functioning as an adhesive). Preferably, a photo-setting resin is used as sealing material 6002. However, a thermosetting resin may be used if the heat resistance of the EL layer is high enough to allow use of such a resin. It is desirable that the sealing material 6002 has such properties as to inhibit permeation of moisture and oxygen as effectively as possible. A desiccant may be mixed in the sealing material 6002.

Also wiring 4016 is electrically connected to a flexible printed circuit (FPC) 4017 by being passed through a gap between the sealing material 6002 and the substrate 4010. While the electrical connection of the wiring 4016 is described, other wirings 4014a, 4014b, and 4015 are also connected electrically to the FPC 4017 by being passed through the gap between the sealing material 6002 and the substrate 4010.

In Embodiment 6, after the filler material 6004 has been provided, the cover member 6000 is bonded and the frame member 6001 is attached so as to cover the side surfaces (exposed surfaces) of the filler material 6004. However, the filler material 6004 may be provided after attachment of the cover member 6000 and the frame member 6001. In such a case, a filler injection hole is formed which communicates with a gap formed by the substrate 4010, the cover member 6000 and the frame member 6001. The gap is evacuated to produce a vacuum (at 10<sup>-2</sup> Torr or lower), the injection hole is immersed in the filler material in a tank, and the air pressure outside the gap is increased relative to the air pressure in the gap, thereby filling the gap with the filler 20 material.

The present embodiment can be freely combined with Embodiments 1 to 5 to be implemented. (Embodiment 7)

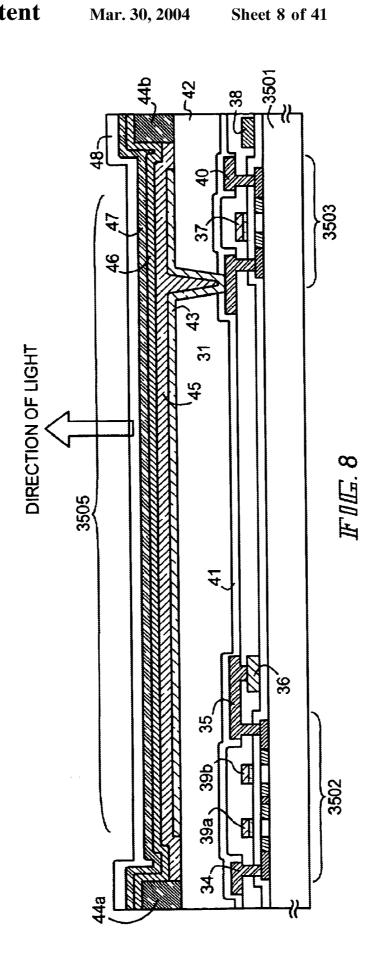

Here, FIG. 8 illustrates a further detailed structure in cross 25 section of a pixel portion of an EL display device.

It is to be noted that the present embodiment illustrates a pixel structure of Embodiment 1 of a pixel structure according to the present invention which corresponds to a case where power supply lines in parallel with source signal lines 30 are formed in a layer forming the source signal lines and power supply lines in parallel with gate signal lines are formed in a layer forming the gate signal lines.

In FIG. 8, a TFT 3502 for switching provided on a tionally. In the present embodiment, the TFT 3502 is of a double gate structure having gate electrodes 39a and 39b. By adopting the double gate structure, two TFTs are substantially connected in series, and thus, there is an advantage that an off current value can be decreased. It is to be noted that, though the double gate structure is adopted in the present embodiment, a single gate structure, a triple gate structure, or a multiple gate structure having more than three gates may also be adopted. Further, a p-channel type TFT formed conventionally may also be used.

In the present embodiment, a TFT 3503 for driving is an n-channel type TFT formed conventionally. A gate electrode 37 of the TFT 3503 for driving is electrically connected to a drain wiring 35 of the TFT 3502 for switching via a wiring 36. 34 is a source signal line.

Since the TFT for driving is an element for controlling the amount of electric current through the EL element, a lot of electric current passes through it, and thus, it is highly liable to deterioration due to heat or due to hot carrier. Therefore, a structure where an LDD region is provided on the side of a drain of the TFT for driving so as to overlap the gate electrode through a gate insulating film is quite effective.

Further, a single gate structure of the driver TFT 3503 is shown in the figures in this embodiment, but a multi-gate structure in which a plurality of TFTs are connected in series may also be used. In addition, a structure in which a plurality of TFTs are connected in parallel, effectively partitioning into a plurality of channel forming regions, and which can perform radiation of heat with high efficiency, may also be used.

Further, a source wiring 40 is connected to a power supply line 38 formed in a layer forming the gate electrodes 37 ad 16

39, and constant voltage is always applied to the source wiring 40. Here, a power supply line is formed also in a layer forming the source wiring 40 and the source signal line 34, and is electrically connected through a contact hole to the power supply line 38, though not shown in the figure.

A first passivation film 41 is formed on the switching TFT 3502 and the driver TFT 3503, and a leveling film 42 comprising an insulating resin film is formed on the first passivation film 41. It is extremely important to level the step due to the TFTs using the leveling film 42. An EL layer formed later is extremely thin, so there are cases in which defective light emissions occur. Therefore, to form the EL layer with as level a surface as possible, it is preferable to perform leveling before forming a pixel electrode.

Furthermore, reference numeral 43 denotes a pixel electrode (EL element cathode in this case) made from a conducting film with high reflectivity, and this is electrically connected to a drain region of the driver TFT 3503. It is preferable to use a low resistance conducting film, such as an aluminum alloy film, a copper alloy film, and a silver alloy film, or a laminate of such films. Of course, a lamination structure with another conducting film may also be used.

In addition, a light emitting layer 45 is formed in the middle of a groove (corresponding to a pixel) formed by banks 44a and 44b, which are formed by insulating films (preferably resins). Note that only one pixel is shown in the figures here, but the light emitting layer may be divided to correspond to each of the colors R (red), G (green), and B (blue). A  $\pi$  conjugate polymer material is used as an organic EL material. Polyparaphenylene vinylenes (PPVs), polyvinyl carbazoles (PVKs), and polyfluoranes can be given as typical polymer materials.

Note that there are several types of PPV organic EL substrate 3501 is an n-channel type TFT formed conven- 35 materials, and materials recorded in Shenk, H., Becker, H., Gelsen, O., Kluge, E., Kreuder, W., and Spreitzer, H., "Polymers for Light Emitting Diodes", Euro Display Proceedings, 1999, pp. 33-7, and in Japanese Patent Application Laid-open No. Hei 10-92567, for example, may be

> As specific light emitting layers, cyano-polyphenylene vinylene may be used as a red light emitting layer, polyphenylene vinylene may be used as a blue light emitting layer, and polyphenylene vinylene or polyalkylphenylene may be 45 used as a red light emitting layer. The film thickness may be between 30 and 150 nm (preferably between 40 and 100 nm).

However, the above example is one example of the organic EL materials which can be used as luminescence layers, and it is not necessary to limit use to these materials. An EL layer may be formed by freely combining light emitting layers, electric charge transporting layers, and electric charge injecting layers.

For example, embodiment 4 shows an example of using polymer material as a light emitting layer, but a low molecular weight organic EL material may also be used. Further, it is possible to use inorganic materials such as silicon carbide, as an electric charge transporting layer or an electric charge injecting layer. Known materials can be used for these organic EL materials and inorganic materials.

A laminate structure EL layer, in which a hole injecting layer 46 made from PEDOT (polythiophene) or PAni (polyaniline) is formed on the light emitting layer 45, is used in embodiment 4. An anode 47 is then formed on the hole injecting layer 46 from a transparent conductive film. The light generated by the light emitting layer 45 is radiated toward the upper surface (opposite the direction to the

substrate 3501 where TFT is formed) in this embodiment, and therefore the anode must have a conductive property and be formed of a material having a property of being transparent to light. An indium oxide and tin oxide compound, or an indium oxide and zinc oxide compound can be used as the transparent conductive film. However, because it is formed after forming the low heat resistance light emitting and hole injecting layers, it is preferable to use a material which can be deposited at as low a temperature as possible.

An EL element 3505 is complete at the point where the 10 anode 47 is formed. Note that what is called the EL element 3505 here is formed by the pixel electrode (anode) 43, the light emitting layer 45, the hole injecting layer 46, and the anode 47. The pixel electrode 43 is nearly equal in area to EL device. Therefore, the light emitting efficiency is extremely high, and a bright image display becomes pos-

In addition, a second passivation film 48 is then formed on the anode 47 in this embodiment. It is preferable to use a 20 silicon nitride film or an oxidized silicon nitride film as the second passivation film 48. The purpose of this is the isolation of the EL element from the outside, and this is meaningful in preventing degradation due to oxidation of the organic EL material, and in controlling gaseous emitted from the organic EL material. The reliability of the EL display can thus be raised.

The EL display device of the present invention has a pixel portion made from pixels structured as in FIG. 8, and has a switching TFT with a sufficiently low off current value, and a current control TFT which is strong with respect to hot carrier injection. An EL device having high reliability, and in which good image display is possible, can therefore be

this embodiment by freely combining it with the constitutions of any of Embodiments 1 to 6. (Embodiment 8)

In this embodiment, there will be described a structure in which the structure of the EL element **3505** is reversed in the pixel portion illustrated in Embodiment 7. Explanation will be given with reference to FIG. 9. Note that since the points of difference from the structure shown in FIG. 8 lie only in parts of the EL element 3701 and the driver TFT 3553, the others shall be omitted from description.

Referring to FIG. 9, a driver TFT 3553 is formed using the p-channel TFT manufactured by known method. Note that the driver TFT is not limited to a p-channel TFT and n-channel TFT may be used.

In this embodiment, a transparent conductive film is 50 employed as a pixel electrode (anode) 50. Concretely, the conductive film is made of a compound of indium oxide and zinc oxide. Of course, a conductive film made of a compound of indium oxide and tin oxide may well be employed.

Besides, after banks 51a and 51b made of an insulating film have been formed, a light emitting layer 52 made of polyvinylcarbazole is formed on the basis of the application of a solution. The light emitting layer 52 is overlaid with an electron injection layer 53 made of potassium acetylacetonate (expressed as acacK), and a cathode 54 made of an aluminum alloy. In this case, the cathode 54 functions also as a passivation film. Thus, an EL element 3701 is formed.

In the case of this embodiment, light generated by the light emitting layer 52 is radiated toward a substrate 3501 formed with TFTs as indicated by an arrow.

The present embodiment can be freely combined with Embodiments 1 to 6 to be implemented.

18

(Embodiment 9)

Although FIGS. 2, 3, 10 and 42 to 44 show the structure in which the storage capacitor is provided to hold the voltage applied to the gate electrode of the driver TFT, the storage capacitor can also be omitted.

In the case where the n-channel TFT used as a driver TFT has the LDD region which is provided so as to overlap with the gate electrode through the gate insulating film. Although a parasitic capacitance generally called a gate capacitance is formed in this overlapping region, this embodiment is characterized in that this parasitic capacitance is positively used as a capacitor to hold a voltage applied to a gate electrode of the driver TFT.

Since the capacity of this parasitic capacitance is changed the pixel, and consequently the entire pixel functions as an 15 by the overlapping area of the gate electrode and the LDD region, it is determined by the length of the LDD region contained in the overlapping region.

> The present embodiment can be freely combined with Embodiments 1 to 8 to be implemented. (Embodiment 10)

> In this embodiment, a method of manufacturing the pixel portion of an EL display device in accordance with the present invention and a TFT of a driver circuit portion which is provided in the periphery of the pixel portion. Note that a CMOS circuit is shown in the figures as a basic unit for a driving circuit in order to simplify the explanation.

First, as shown in FIG. 11A, a substrate 501, on the surface of which a base film (not shown in the figures) is formed, is prepared. A 100 nm thick silicon nitride oxide film and a 200 nm thick silicon nitride oxide film are laminated and used as the base film on crystallized glass in Embodiment 10. At this point it is appropriate to set the nitrogen concentration of the film contacting the crystallized glass substrate to between 10 and 25 wt %. Elements may Note that it is possible to implement the constitution of 35 also, of course, be formed directly on top of a quartz substrate without forming the base film.

> Next, an amorphous silicon film 502 with a thickness of 45 nm is formed on the substrate 501 by a known film deposition method. Note that it is not necessary to limit this to the amorphous silicon film, and any other film, provided that it is a semiconductor film having an amorphous structure (including a microcrystalline semiconductor film) may also be used. In addition, a compound semiconductor film containing an amorphous structure, such as an amorphous 45 silicon germanium film, may also be used.

The process from here to FIG. 11C may be completely cited from Japanese Patent Application Laid-open No. Hei 10-247735 of the present applicant. In this publication, a technique regarding a method of crystallizing a semiconductor film by using an element such as Ni or the like, as a catalyst is disclosed.

First, a protecting film **504** having opening portions **503***a* and 503b is formed. A 150 nm thick silicon oxide film is used in Embodiment 10. A layer containing nickel (Ni) 505 (Ni containing layer) is then formed on the protecting film 504 by spin coating. The above publication may be referred to regarding the formation of the Ni containing layer.

Next, as shown in FIG. 11B, the amorphous silicon film **502** is crystallized by heat treatment for 14 hours at 570° C. in an inert atmosphere. Crystallization proceeds roughly parallel to the substrate with regions in contact with Ni (hereafter referred to as Ni added regions) 506a and 506b as origins, forming a polysilicon film 507 having a crystal structure in which bar-shaped crystals are lined up together.

An element residing in periodic table group 15 (preferably phosphorous) is then added to the Ni added regions 506a and **506***b* with the protecting film **504** left in place as a mask, as

(PH<sub>3</sub>). Ion implantation, which performs separation of mass, may also be used, of course.

shown in FIG. 11C. Regions in which a high concentration of phosphorous is added (hereafter referred to as phosphorous added regions) 508a and 508b are thus formed.

Next, as shown in FIG. 11C, a heat treatment is added for 12 hours at 600° C. in an inert atmosphere. The Ni which 5 exists in the polysilicon film 507 migrates due to the heat treatment, and finally, is nearly completely captured in the phosphorous added regions 508a and 508b, as shown by the arrows. This can be considered to be a phenomenon of a gettering effect of the metal element (Ni in embodiment 10) 10 by phosphorous.

The concentration of Ni remaining in the polysilicon film 509 by this process is reduced at least to  $2\times10^{17}$  atoms/cm³, as measured by SIMS (secondary ion mass spectroscopy). Ni is a lifetime killer for the semiconductor, and if the 15 concentration of Ni is reduced to this level, then there is no harmful influence imparted to the characteristics of a TFT. Further, this concentration is nearly at the limit of measurability by current SIMS, and therefore it is anticipated that there is an even lower actual concentration (not more than  $20\times10^{17}$  atoms/cm³).

The polysilicon film 509, crystallized by using a catalyst, and in which the catalyst is then reduced to a level at which it does not cause damage to the function of the TFT, is thus obtained. Active layers 510 to 513 using only the polysilicon film 509 are formed afterward by patterning. Note that a marker for performing mask alignment during later patterning may be formed at this time using the above polysilicon film. (See FIG. 11D.)

A 50 nm thick silicon nitride oxide film is formed next by 30 plasma CVD, as shown in FIG. 11E, and moreover, a thermal oxidation step is performed by heat treatment for 1 hour at 950° C. in an oxidizing atmosphere. Note that the oxidizing environment may be an oxygen atmosphere, or an oxygen atmosphere in which a halogen element is added.

Oxidation proceeds in the interface of the active layers and the above silicon nitride oxide film by the above thermal oxidation step, and an approximately 15 nm thickness of the polysilicon film is oxidized, forming an approximately 30 nm thick silicon oxide film. In other words, a gate insulating film 514 with a thickness of 80 nm is formed from a lamination of the 30 nm thick silicon oxide film and the 50 nm thick silicon nitride oxide film.

A resist masks 515a and 515b is formed next, as shown in FIG. 12A, and an impurity element which imparts p-type 45 conductivity (hereafter referred to as a p-type impurity element) is added through the gate insulating film 514. An element residing in periodic table group 13, typically boron or gallium, can be used as the p-type impurity element. This process is (referred to as a channel doping process) is a 50 process for controlling the threshold voltage of the TFT.

Note that boron is added in Embodiment 10 by plasma excited ion doping, without separation of mass, of diborane  $(B_2H_6)$ . Ion implantation, which performs separation of mass, may of course also be used. Impurity regions **516** and **517**, containing boron at a concentration of  $1 \times 10^{15}$  to  $1 \times 10^{18}$  atoms/cm<sup>3</sup> (typically between  $5 \times 10^{16}$  and  $5 \times 10^{17}$  atoms/cm<sup>3</sup>) this process.

Resist masks 519a and 519b are formed next, as shown in FIG. 12B, and an impurity element which imparts n-type conductivity (hereafter referred to as an n-type impurity element) is added, through the gate insulating film 514. An element residing in periodic table group 15, typically phosphorous or arsenic, can be used as the n-type impurity element. Note that phosphorous is added at a concentration of  $1 \times 10^{18}$  atoms/cm<sup>3</sup> in Embodiment 10 by plasma excited plasma doping, without separation of mass, of phosphine

The dosage is regulated so that the n-type impurity element is contained in an n-type impurity region 520 formed as above at a concentration of  $2\times10^{16}$  to  $5\times10^{19}$  atoms/cm<sup>3</sup> (typically between  $5\times10^{17}$  and  $5\times10^{16}$  atoms/cm<sup>3</sup>).

A process of activating the added n-type impurity elements and p-type impurity elements is then performed, as shown in FIG. 12C. It is not necessary to place any limitations on the means of activation, but a furnace annealing process using an electric furnace is preferable because the gate insulating film 514 has been formed. Further, there is a possibility of damage being imparted to the interface of the active layers and the gate insulating film of the portion which becomes a channel forming region in the process of FIG. 12A, and therefore it is preferable to perform heat treatment at as high a temperature as possible.

ability by current SIMS, and therefore it is anticipated that there is an even lower actual concentration (not more than  $2\times10^{17}$  atoms/cm³).

The polysilicon film 509, crystallized by using a catalyst, and in which the catalyst is then reduced to a level at which it does not cause damage to the function of the TFT, is thus obtained. Active layers 510 to 513 using only the polysilicon 25 Crystallized glass having a high resistance to heat is used in Embodiment 10, and therefore the activation process is performed by furnace annealing at 800° C. for 1 hour. Note that thermal oxidation may be performed by making the process environment into an oxidizing atmosphere, and that heat treatment may be performed by using an inert atmoobtained. Active layers 510 to 513 using only the polysilicon

The edge portion of the n-type impurity region 520, namely, the boundary (junction portion) with a region in the periphery of the n-type impurity region 520 in which the n-type impurity element is not added (the p-type impurity region formed by the process of FIG. 12A) are defined by the above process. This means that an extremely good junction portion between an LDD region and the channel forming region can be formed at the point when the TFT is later completed.

A 200 to 400 nm thick conductive film is formed next and patterned, forming gate electrodes **522** to **525**. The line width of the gate electrodes **522** to **525** determine the channel length of each TFT

Note that a single layer conductive film may be formed for the gate electrode, but when necessary, it is preferable to use a two layer or a three layer lamination film. A known conductive film can be used as the gate electrode material. Specifically, a film of an element chosen from among the group consisting of tantalum (Ta), titanium (Ti), molybdenum (Mo), tungsten (W), chromium (Cr), and silicon (Si); or a film of a nitrated compound of the above elements (typically a tantalum nitride film, a tungsten nitride film, or a titanium nitride film); or an alloy film of a combination of the above elements (typically a Mo—W alloy or a Mo—Ta alloy); or a silicide film of the above elements (typically a tungsten silicide film or a titanium silicide film) can be used. A single layer film or a lamination may be used, of course.

A lamination film made from a 50 nm thick tungsten nitride (WN) film and a 350 nm thick tungsten (W) film is used in Embodiment 10. This film may be formed by sputtering. Furthermore, if an inert gas such as xenon (Xe) or neon (Ne) is added as a sputtering gas, then film peeling due to stress can be prevented.

The gate electrode **523** is formed at this time so as to overlap portion of the n-type impurity region **520**, with the gate insulating film **514** interposed therebetween. The overlapping portions later become LDD regions overlapping the gate electrode. Note that two gate electrodes **524***a* and **524***b* can be seen in cross section, but they are actually connected electrically.

Next, an n-type impurity element (phosphorous is used in Embodiment 10) is added in a self-aligning manner with the

20

gate electrodes **522** to **525** as masks, as shown in FIG. **13A**. The addition is regulated so that phosphorous is added to impurity regions **526** to **533** thus formed at a concentration of  $\frac{1}{10}$  to  $\frac{1}{2}$  (typically between  $\frac{1}{4}$  and  $\frac{1}{3}$ ) that of Specifically, a concentration of  $1\times10^{16}$  to  $5\times10^{18}$  atoms/cm<sup>3</sup> (typically between  $3\times10^{17}$  and  $3\times10^{18}$  atoms/cm<sup>3</sup>) is preferable.

Resist masks 534a to 534d are formed next, in a shape so as to cover the gate electrodes, as shown in FIG. 13B, and an n-type impurity element (phosphorous is used in Embodiment 10) is added, forming impurity regions 535 to 539 containing a high concentration of phosphorous. Ion doping using phosphine (PH<sub>3</sub>) is also performed here, and the phosphorous concentration of these regions is regulated to be from  $1 \times 10^{20}$  to  $1 \times 10^{21}$  atoms/cm<sup>3</sup> (typically between  $2 \times 10^{20}$  and  $5 \times 10^{20}$  atoms/cm<sup>3</sup>).

A source region or a drain region of the n-channel TFT is formed by this process, and in the switching TFT, a portion of the n-type impurity regions 528 to 531 formed by the process of FIG. 13A remains. These remaining regions correspond to the LDD regions of the switching TFT.

Next, as shown in FIG. 13C, the resist masks 534a to 534d are removed, and a new resist mask 542 is formed. A p-type impurity element (boron is used in Embodiment 10) is then added, forming impurity regions 540, 541, 543 and 544 containing a high concentration of boron. Boron is added here to a concentration of  $3\times10^{20}$  to  $3\times10^{21}$  atoms/cm<sup>3</sup> (typically between  $5\times10^{20}$  and  $1\times10^{21}$  atoms/cm<sup>3</sup>) by ion doping using diborane (B<sub>2</sub>H<sub>6</sub>).

Note that phosphorous has already been added to the impurity regions 540, 541, 543 and 544 at a concentration of  $30 \times 10^{20}$  to  $1\times 10^2$  atoms/cm<sup>3</sup>, but boron is added here at a concentration of at least 3 times that of the phosphorous. Therefore, the n-type impurity regions already formed completely invert to p-type, and function as p-type impurity regions.

Next, after removing the resist mask **542**, as shown in FIG. **13**D, a first interlayer insulating film **546** is formed. A single layer insulating film containing silicon is used as the first interlayer insulating film **546**, but a lamination film of the same may also be used. Further, a film thickness of between 400 nm and 1.5  $\mu$ m is appropriate. A lamination structure of an 800 nm thick silicon oxide film on a 200 nm thick silicon nitride oxide film is used in Embodiment 10.

The n-type impurity elements and the p-type impurity elements, added at their respective concentrations, are acti- 45 vated afterward. Furnace annealing is preferable as a means of activation. Heat treatment is performed using an electric furnace for 4 hours at 550° C. in an inert atmosphere in Embodiment 10.